**EECE416 Microcomputer Fundamentals**

# 68000 Processor

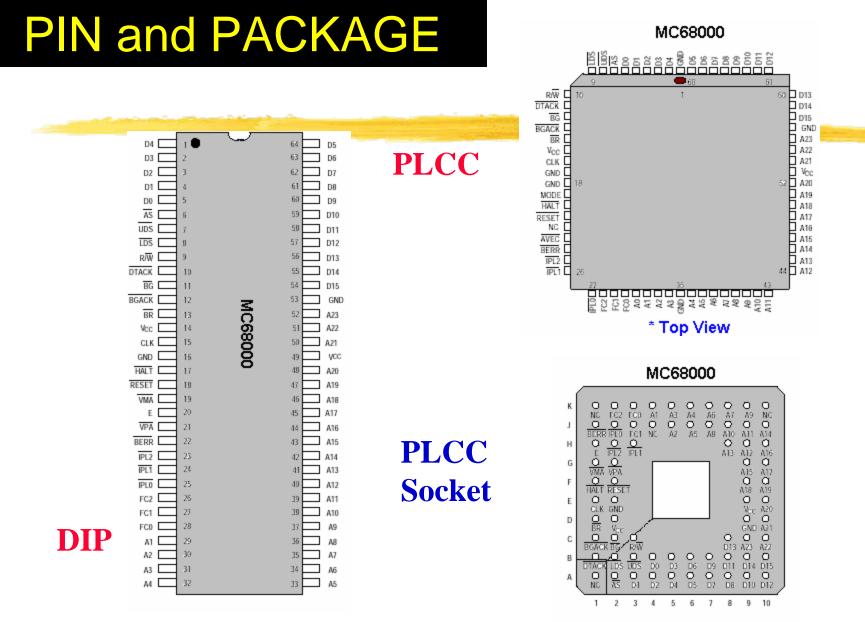

- **1. Chip Signal Description**

- **2. Instruction and Programming**

**Dr. Charles Kim**

**Howard University**

# 68000 Microprocessor

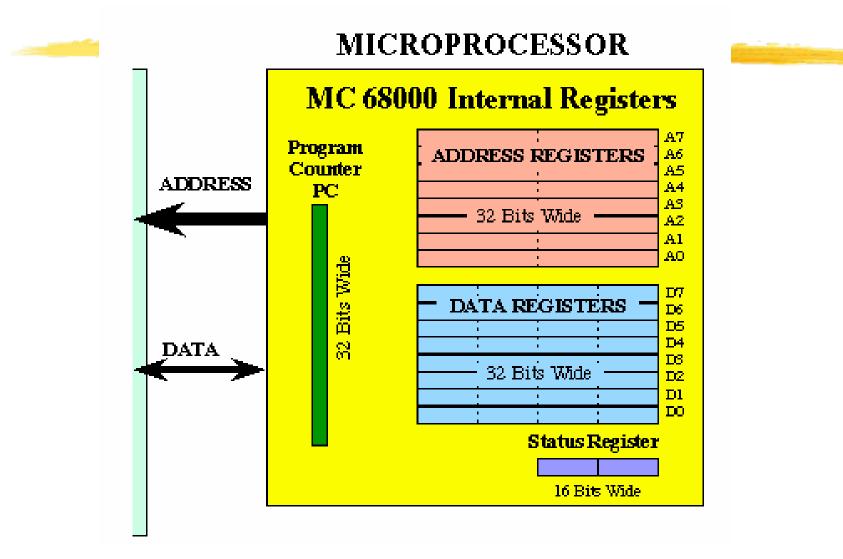

¥64 pins ∺32- bit Data and Address Registers D #16- bit Data Bus ∺24- bit Address Bus (16MB) #14 Addressing Modes Hemory- Mapped Input/ Output **Hereford** Program Counter (PC) **∺**5 Main Data Types- *L*, *W*, *B*, *b*, *BCD* ∺7 interrupt levels Clock speeds: 4MHz to 12.5MHz Synchronous and asynchronous data transfers

|            |   |       |        |    | 1         |            |

|------------|---|-------|--------|----|-----------|------------|

| D4         |   | 1 🔴 👘 | $\sim$ | 64 | Ь         | D5         |

| D3         |   | 2     |        | 63 | F         | D6         |

| D2         |   | 3     |        | 62 | F         | D7         |

| D1         |   | 4     |        | 61 | F         | DB         |

| D0         | Ξ | 5     |        | 60 | F         | D9         |

| AS         |   |       |        | 59 | E         |            |

|            |   | 6     |        | 59 | E         | D10        |

| UDS        |   | 7     |        |    | E         | D11        |

| LDS        |   | 9     |        | 57 | E         | D12        |

| R/W        |   | 9     |        | 56 | $\square$ | D13        |

| TACK       |   | 10    |        | 55 | $\square$ | D14        |

| BG         |   | 11    |        | 54 | $\square$ | D15        |

| GACK       |   | 12    | 2      | 53 |           | GND        |

| BR         |   | 13    | ឹ      | 52 | $\vdash$  | A23        |

| Vcc        |   | 14    | တ္ထိ   | 51 |           | A22        |

| CLK        |   | 15    | 8      | 50 | Þ         | A21        |

| GND        |   | 16    | C68000 | 49 | Þ         | VCC        |

| HALT       |   | 17    | 0      | 49 |           | A20        |

| ESET       |   | 19    |        | 47 | Ь         | A19        |

| VMA        |   | 19    |        | 46 | Б         | A18        |

| E          |   | 20    |        | 45 | F         | A17        |

| <b>VPA</b> |   | 21    |        | 44 | F         | A16        |

| BERR       |   | 22    |        | 43 | F         | A15        |

| IPL2       |   | 23    |        | 42 | F         | A14        |

| IPL2       | Ξ | 24    |        | 41 | F         | A14<br>A13 |

|            | Γ |       |        |    | E         |            |

| IPL0       | Γ | 25    |        | 40 | E         | A12        |

| FC2        |   | 25    |        | 39 | E         | A11        |

| FC1        |   | 23    |        | 39 | E         | A10        |

| FC0        |   | 28    |        | 37 | Ľ         | A9         |

| A1         |   | 29    |        | 36 |           | A8         |

| A2         |   | 30    |        | 35 |           | A7         |

| A3         |   | 31    |        | 34 |           | A6         |

| A4         |   | 32    |        | 33 | $\square$ | A5         |

|            |   |       |        |    |           |            |

\* Bottom View

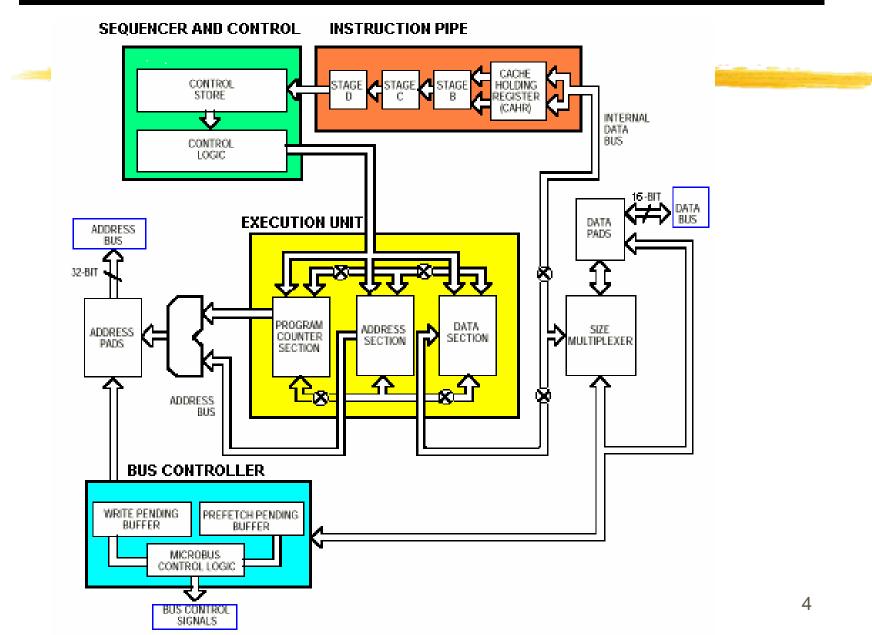

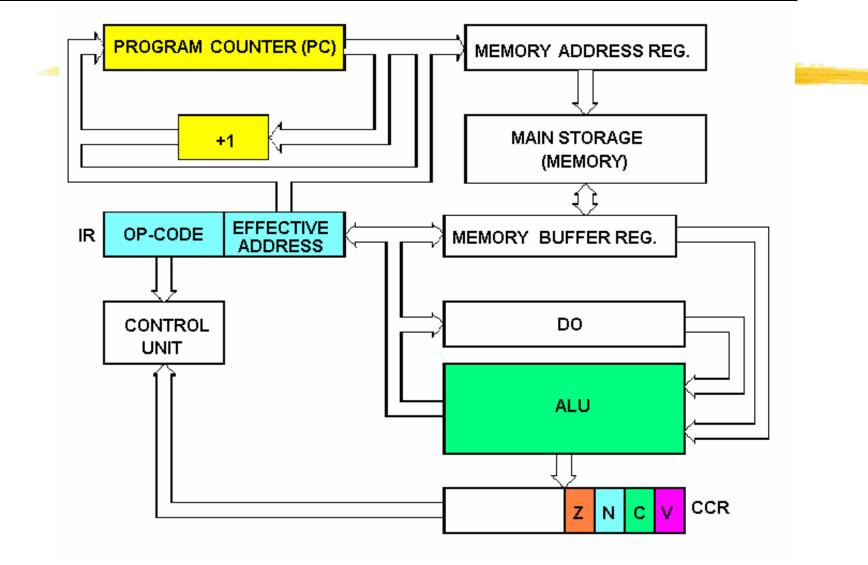

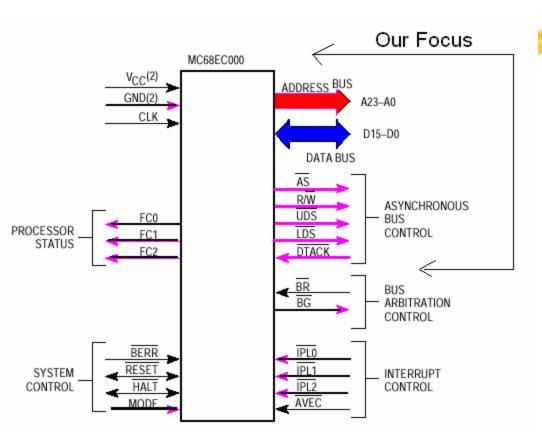

## **BLOCK Diagram**

#### **Core Structure**

# **Internal Structure - Registers**

## Connecting with Memory, I/O, and Peripherals

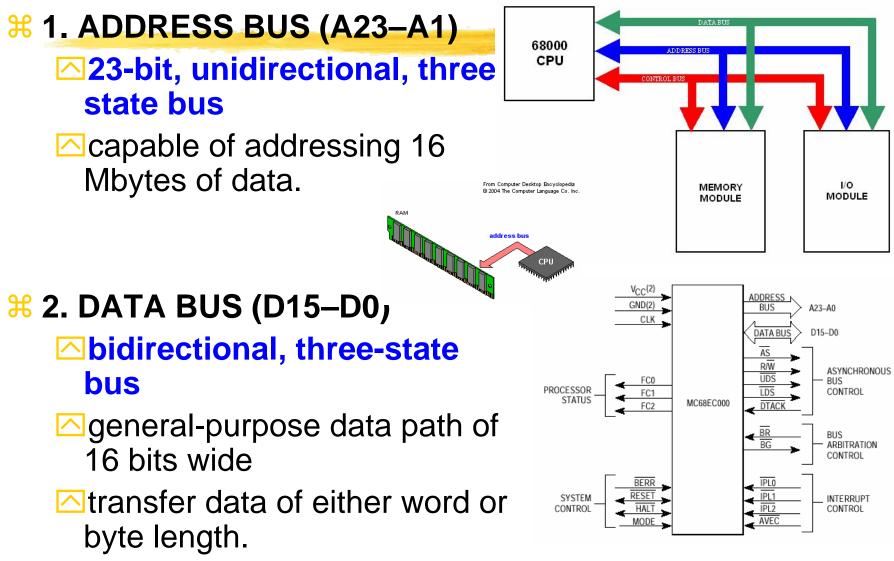

# SIGNAL DESCIRPTION

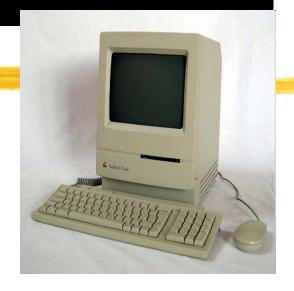

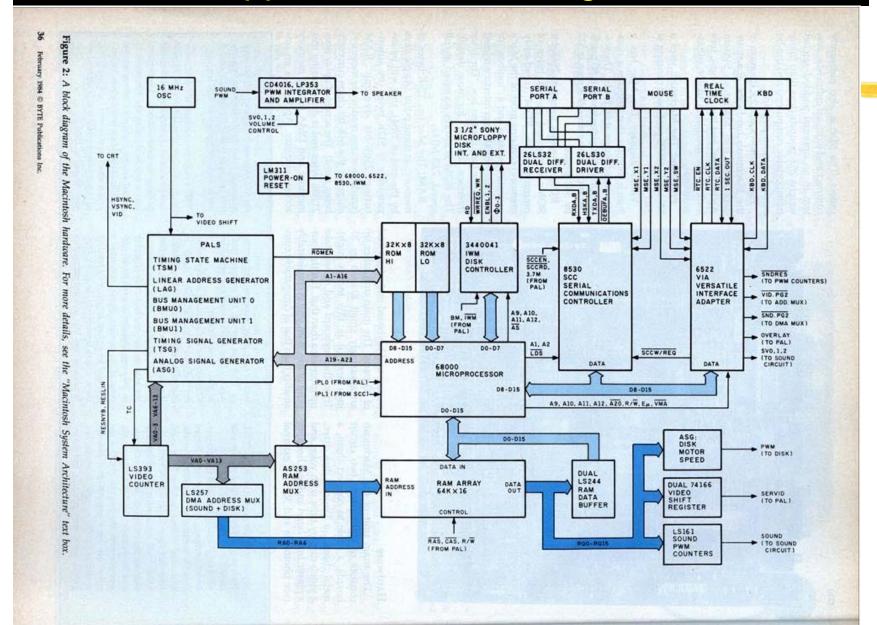

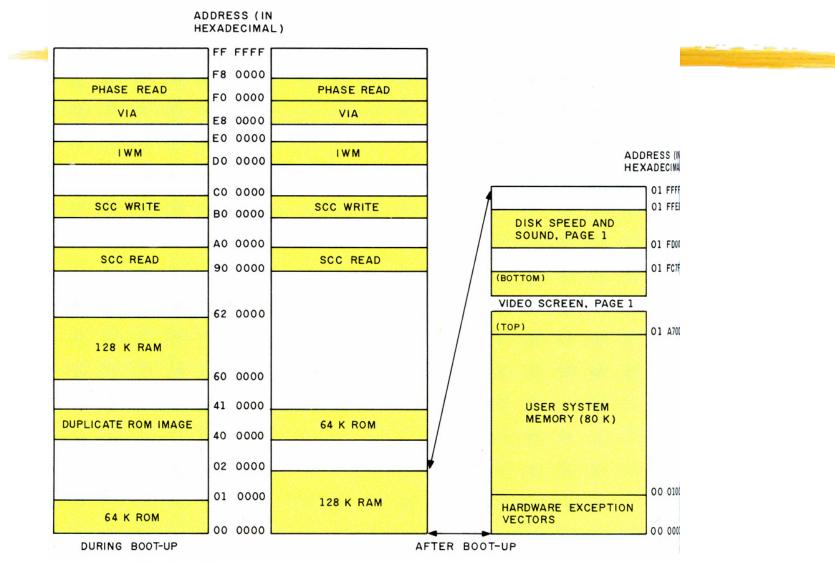

# **Apple Mac**

- ₭ CPU: 8MHz Motorola 68000

- # Introduced in 1984

- Memory: 128KB (512KB in later version) RAM, 64KB ROM

- ₭ 3.5″ 400KB Floppy Disk

- ₭ Application: MacWrite and MacPaint

- ₭ Mouse

- ¥ 9″ B&W Monitor

- ₭ Keyboard

- ₭ Serial Port (DB-9)

- **#** Printer Port

- ₭ Addressing: 24-bit

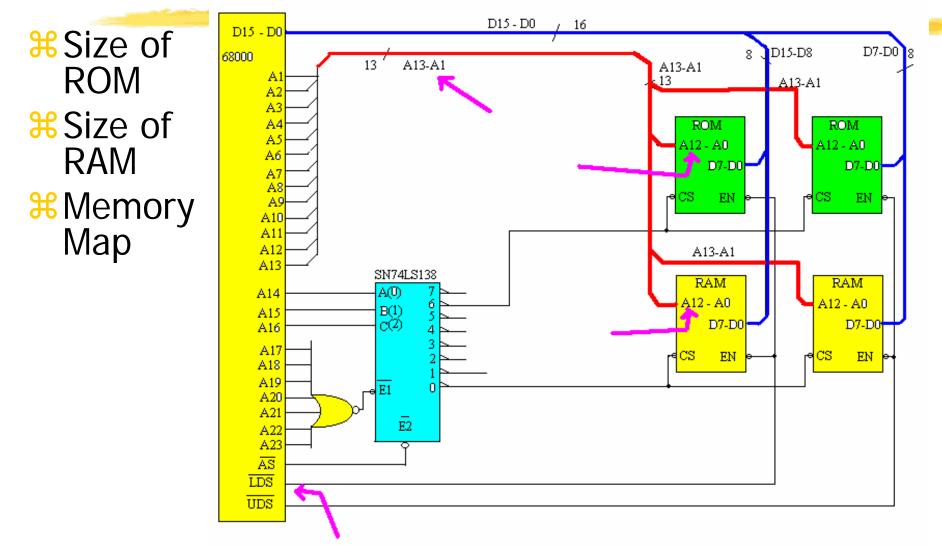

#### **Apple Mac Circuit Diagram**

# Signal Description

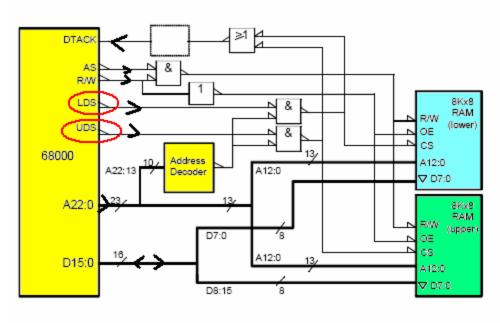

#### 3. ASYNCHRONOUS BUS CONTROL

#### Address Strobe (~AS).

This three-state signal indicates that the information on the address bus is a valid address.

#### △ Read/Write (R/~W).

- This three-state signal defines the data bus transfer as a read or write cycle.

- Upper And Lower Data Strobes (~UDS, ~LDS).

- Data Transfer Acknowledge (~DTACK).

- ☑ This input signal indicates the completion of the data transfer.

Strobe: a signal that is sent to validates data or other signals

# **Memory Access Timing**

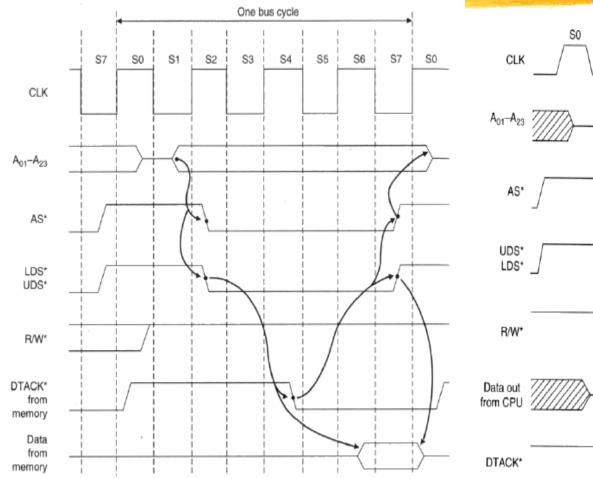

## Read (to CPU) Cycle

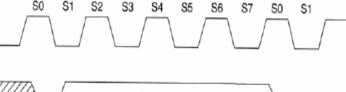

## Write (to Mem) Cycle

## **Other Signals**

#### **4. BUS ARBITRATION CONTROL**

- Bus Request (~BR)

- Bus Grant (~BG)

- Bus Grant Acknowledge (~BGACK)

- % 5. INTERRUPT CONTROL (IPL0,IPL1,IPL2)

- These input signals indicate the encoded priority level of the device requesting an interrupt.

- Level seven, which cannot be masked, has the highest priority; level zero indicates that no interrupts are requested.

- ☐ IPL0 is the least significant bit of the encoded level, and IPL2 is the most

significant bit.

#### **7. M6800 PERIPHERAL CONTROL**

- 🔼 Enable (E)

- Valid Peripheral Address (~VPA)

- Valid Memory Address (~VMA)

#### **6. SYSTEM CONTROL**

- Bus Error (~BERR)

- Reset (~RESET)

- The processor assertion of ~RESET (from executing a ~RESET instruction) resets all external devices of a system without affecting the internal state of the processor.

- Halt (~HALT)

- An input to this bidirectional signal causes the processor to stop bus activity at the completion of the current bus cycle.

- 8. PROCESSOR FUNCTION CODES (FC0, FC1, FC2)

- 8. CLOCK (CLK): 8MHz

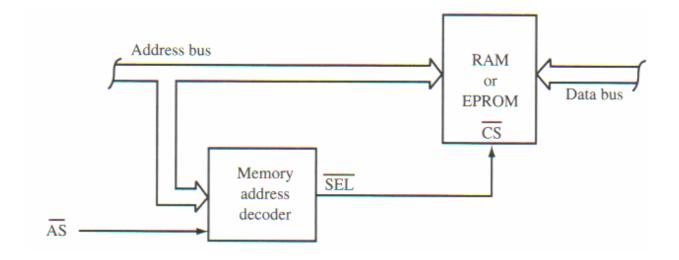

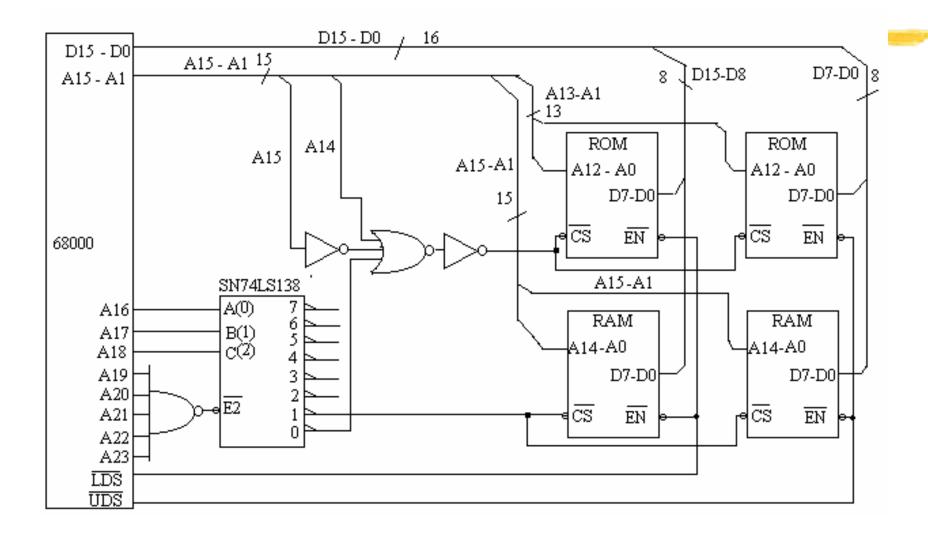

## **Memory Address Decoding**

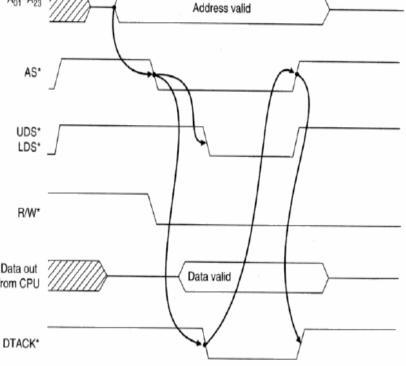

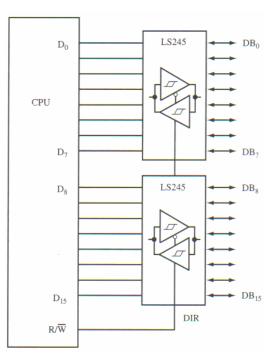

## **Hemory Bus** △Data (Bi-directional) Address (Unidirectional) **H**Address Bus Buffering Fan Out △74LS244 Octal line driver/receiver H Data Bus Buffering R/W for Direction Fan Out △74LS245 Octal Bus Transceiver

# Memory Map (for Apple Mac)

# **Memory Address Decoding**

- ∺ How Much Memory?

- How Many Address Lines?

- 1K  $\rightarrow$  10 lines

- $32K \rightarrow 15$  lines

- $\approx$  23 ADDR lines  $\rightarrow$  8MB?

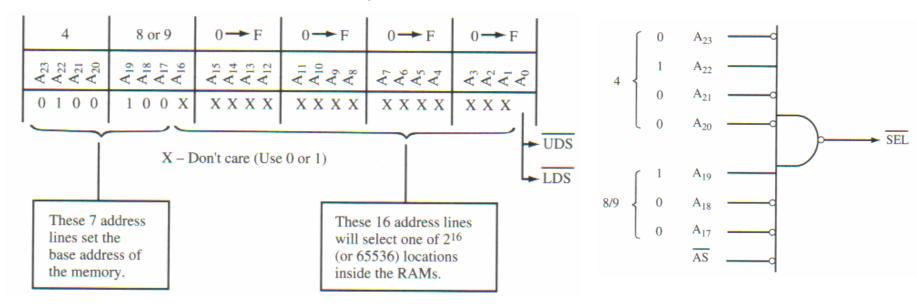

# UDS and LDS

Upper Data Strobe

- △ For accessing upper byte of

- memory

- D15 D8 part of CPU

- □ D7 D0 part of memory

- Lower Data Strobe

- ➢ For accessing lower byte of memory

- ☑ D7-D0 part of CPU

- D7 D0 part of Memory

- **#** Both together works as A0 line

## **Memory Decoding**

# C: 64K Word (or 128 KB) of RAM, with it's starting address at \$480000 A: 128KB → 17 lines Range: \$480000 - \$49FFFF UDS and LDS for A₀ line.

# Memory Decoding Example

₩Q: 16K Word ROM with starting address at \$300000.

## Memory Decoding with Byte/Word Access

### Can You Draw a Memory Map of this?

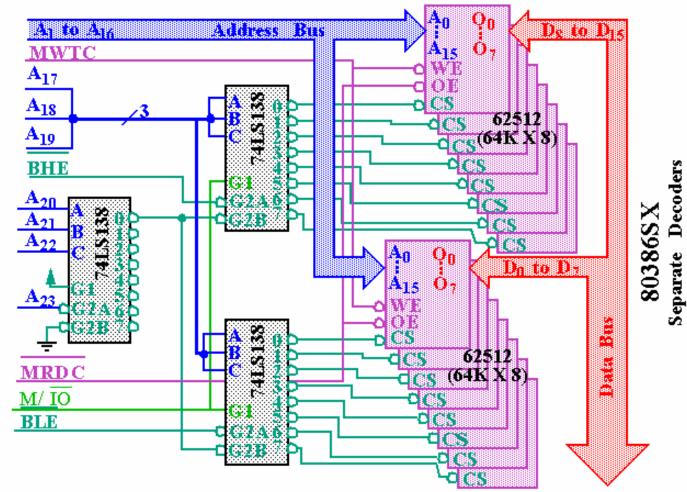

# How about Intel 80386 case?

#### 80386SX 16-bit Memory Interface (Separate Decoders)

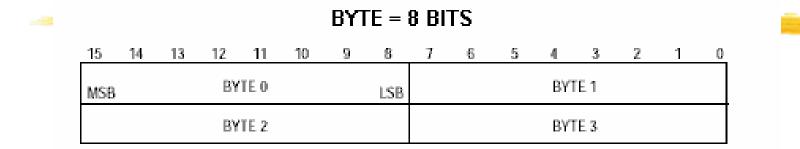

# **Data Organization in Memory**

#### WORD =16 BITS

| 15                 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------------------|----|----|----|----|----|---|----|------|---|---|---|---|---|---|-----|

| MSE                | 3  |    |    |    |    |   | WO | RD 0 |   |   |   |   |   |   | LSB |

|                    |    |    |    |    |    |   | WO | RD 1 |   |   |   |   |   |   |     |

| WORD 2             |    |    |    |    |    |   |    |      |   |   |   |   |   |   |     |

| EVEN BYTE ODD BYTE |    |    |    |    |    |   |    |      |   |   |   |   |   |   |     |

| 7                  | 6  | 5  | 4  | 3  | 2  | 1 | 0  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

# Data/Address Organization in Memory

#### LONG WORD = 32 BITS

| 15  | 14 | 13   | 12   | 11  | 10 | 9 | 8    | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-----|----|------|------|-----|----|---|------|-------|---|---|---|---|---|---|-----|

| MSB |    | LONG | WODD |     |    |   | HIGH | ORDE  | 2 |   |   |   |   |   |     |

|     |    | LONG | WORD |     |    |   | LOW  | ORDER | 2 |   |   |   |   |   | LSB |

|     |    | LONG | WORD | 1 - |    |   |      |       |   |   |   |   |   |   |     |

|     |    | LONG | WORD | 2 - |    |   |      |       |   |   |   |   |   |   |     |

#### ADDRESS = LONG WORD = 32 BITS

| 15  | 14 | 13  | 12     | 11 | 10 | 9 | 8    | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-----|----|-----|--------|----|----|---|------|-------|---|---|---|---|---|---|-----|

| MSB |    | ADD | RESS 0 | _  |    |   | HIGH | ORDE  | 2 |   |   |   |   |   |     |

|     |    | NDD | NE33 V |    |    |   | LOW  | ORDEF | ł |   |   |   |   |   | LSB |

|     |    | ADD | RESS 1 | -  |    |   |      |       |   |   |   |   |   |   |     |

|     |    | ADD | RESS 2 | _  |    |   |      |       |   |   |   |   |   |   |     |

# **Big-Endian**

- Hords are stored with the lower 8- bits in the higher of the two storage locations

- Section 12 Constraints and the lowest addr) processors, like the Intel 80x86 family

| Word Data Byte1 Byte0        |                    |                      |       |       |  |  |  |  |  |  |  |  |

|------------------------------|--------------------|----------------------|-------|-------|--|--|--|--|--|--|--|--|

| Store the Word data at \$0   |                    |                      |       |       |  |  |  |  |  |  |  |  |

| Memory<br>address            |                    | Memory<br>address    |       |       |  |  |  |  |  |  |  |  |

| \$000000 Byte0 Byte1         |                    | \$000000             | Byte1 | Byte0 |  |  |  |  |  |  |  |  |

| \$000002<br>\$000004         |                    | \$000002<br>\$000004 |       |       |  |  |  |  |  |  |  |  |

|                              |                    |                      |       |       |  |  |  |  |  |  |  |  |

| \$000000 <b>10 32</b>        | MOVE \$3210, 0     | \$000000             | 32    | 10    |  |  |  |  |  |  |  |  |

| \$000000 <u>10</u> <u>32</u> | MOVE \$76543210, 0 | \$000000             | 76    | 54    |  |  |  |  |  |  |  |  |

| \$000002 54 76               | 11012 0,0010210, 0 | \$000002             | 32    | 10    |  |  |  |  |  |  |  |  |

|                              |                    |                      |       |       |  |  |  |  |  |  |  |  |

| Little-Endian                |                    | Big-Endian           |       |       |  |  |  |  |  |  |  |  |

| Intel                        |                    | Motorola             |       |       |  |  |  |  |  |  |  |  |

|                              |                    |                      |       |       |  |  |  |  |  |  |  |  |