### **Timing without using Timer**

WWW.MWFTR.COM

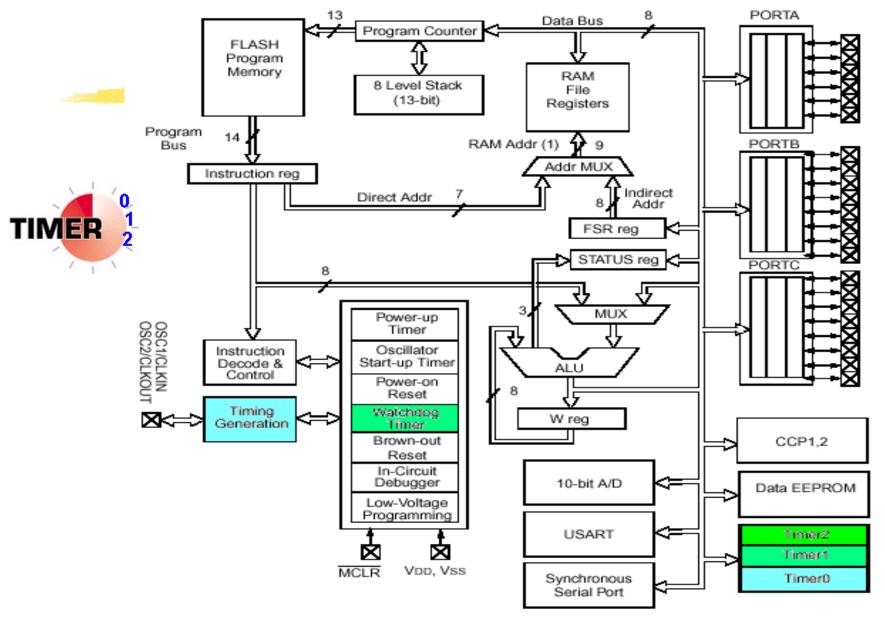

### **16F877 TIMER Modules**

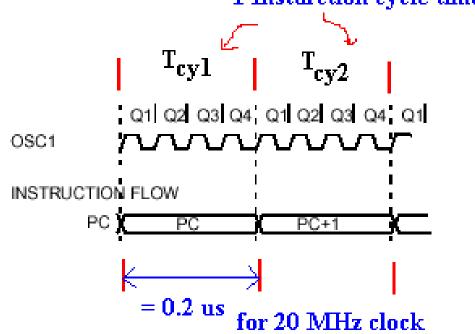

### **Clocking Scheme and Instruction Cycle**

- # The Clock input is divided by 4 internally

- # Four Quadrature clocks: Q1,Q2, Q3, and Q4

- # An "Instruction cycle" consists of 4 quadrature clocks.

- ## All instructions are single cycle, except for any program branches.

1 Insturction cycle time

# **Instruction Cycles**

| Mnemonic,<br>Operands                  |      | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |  |

|----------------------------------------|------|------------------------------|--------|---------------|------|------|------|----------|-------|--|

|                                        |      |                              |        | MSb           |      |      | LSb  | Affected | Notes |  |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                              |        |               |      |      |      |          |       |  |

| ADDWF                                  | f, d | Add W and f                  | 1      | 0.0           | 0111 | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF                                  | f, d | AND W with f                 | 1      | 0.0           | 0101 | dfff | ffff | Z        | 1,2   |  |

| CLRF                                   | f    | Clear f                      | 1      | 0.0           | 0001 | lfff | ffff | Z        | 2     |  |

| CLRW                                   | -    | Clear W                      | 1      | 0.0           | 0001 | 0xxx | xxxx | Z        |       |  |

| COMF                                   | f, d | Complement f                 | 1      | 0.0           | 1001 | dfff | ffff | Z        | 1,2   |  |

| DECF                                   | f, d | Decrement f                  | 1      | 0.0           | 0011 | dfff | ffff | Z        | 1,2   |  |

| DECFSZ                                 | f, d | Decrement f, Skip if 0       | 1(2)   | 0.0           | 1011 | dfff | ffff |          | 1,2,3 |  |

| INCF                                   | f, d | Increment f                  | 1      | 0.0           | 1010 | dfff | ffff | Z        | 1,2   |  |

| INCFSZ                                 | f, d | Increment f, Skip if 0       | 1(2)   | 0.0           | 1111 | dfff | ffff |          | 1,2,3 |  |

| IORWF                                  | f, d | Inclusive OR W with f        | 1      | 0.0           | 0100 | dfff | ffff | Z        | 1,2   |  |

| MOVF                                   | f, d | Move f                       | 1      | 0.0           | 1000 | dfff | ffff | Z        | 1,2   |  |

| MOVWF                                  | f    | Move W to f                  | 1      | 0.0           | 0000 | lfff | ffff |          | ·     |  |

| NOP                                    | -    | No Operation                 | 1      | 0.0           | 0000 | 0xx0 | 0000 |          |       |  |

| RLF                                    | f, d | Rotate Left f through Carry  | 1      | 0.0           | 1101 | dfff | ffff | С        | 1,2   |  |

| RRF                                    | f, d | Rotate Right f through Carry | 1      | 0.0           | 1100 | dfff | ffff | С        | 1,2   |  |

| SUBWF                                  | f, d | Subtract W from f            | 1      | 0.0           | 0010 | dfff | ffff | C.DC.Z   | 1,2   |  |

| SWAPF                                  | f, d | Swap nibbles in f            | 1      | 0.0           | 1110 | dfff | ffff |          | 1,2   |  |

| XORWF                                  | f, d | Exclusive OR W with f        | 1      | 0.0           | 0110 | dfff | ffff | Z        | 1,2   |  |

| BIT-ORIENTED FILE REGISTER OPERATIONS  |      |                              |        |               |      |      |      |          |       |  |

| BCF                                    | f, b | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |  |

| BSF                                    | f, b | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |  |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |  |

| BTFSS                                  | f, b | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |  |

| LITERAL AND CONTROL OPERATIONS         |      |                              |        |               |      |      |      |          |       |  |

| ADDLW                                  | k    | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW                                  | k    | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |  |

| CALL                                   | k    | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |  |

| CLRWDT                                 | -    | Clear Watchdog Timer         | 1      | 0.0           | 0000 | 0110 | 0100 | TO,PD    |       |  |

| GOTO                                   | k    | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |  |

| IORLW                                  | k    | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |  |

| MOVLW                                  | k    | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |  |

| RETFIE                                 | -    | Return from interrupt        | 2      | 0.0           | 0000 |      | 1001 |          |       |  |

| RETLW                                  | k    | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |  |

| RETURN                                 | -    | Return from Subroutine       | 2      | 0.0           | 0000 | 0000 | 1000 | l        |       |  |

| SLEEP                                  | -    | Go into standby mode         | 1      | 0.0           | 0000 | 0110 | 0011 | TO,PD    |       |  |

| SUBLW                                  | k    | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |  |

| XORLW                                  | k    | Exclusive OR literal with W  | 1      | 11            | 1010 | kkkk | kkkk | Z        |       |  |

## 120 us Dealy

### # 120 us delay

- needs 600 instruction cycles

- 600 = 199\*3 + 3

- Number of Loops=199=0xC7

- $\triangle$  or =198\*3 +6

- Number of Loops=198=0xC6

- $\triangle$  or = 197\*3 +9

- Number of Loops=197=0xC5

| MAIN       | CALL                     | DELAY120us       | 2                 |

|------------|--------------------------|------------------|-------------------|

| SUBROUTINE |                          |                  |                   |

| DELAY120us | MOVLW<br>MOVWF           | L120us<br>N120us | 1<br>1            |

| AGAIN      | DECFSZ<br>GOTO<br>RETURN | N120us<br>AGAIN  | ₹1<br>2<br>2<br>1 |

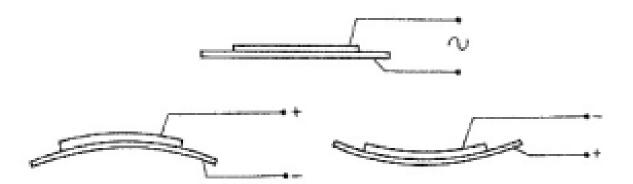

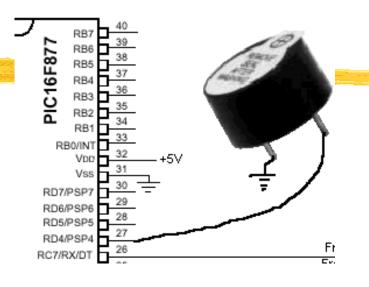

## Piezo Buzzer

#### CE-328 Series

color Black Noryl Housing Material Pin Terminal

#### **ELECTRICAL SPECIFICATIONS**

| MODEL NO.             | 3254120    |           |

|-----------------------|------------|-----------|

| Operating Voltage     | (VDC)      | 3 - 16    |

| Rated Voltage         | (VDC)      | 12        |

| *Max. Rated Current   | (mA.)      | 7         |

| *Min. Sound Output (  | (dBA/10cm) | 80        |

| *Frequency            | (Hz.)      | 4000±500  |

| Tone Nature           |            | single    |

| Operating Temperature | e (°C)     | -20 - +60 |

| Weight                | (gm.)      | 1         |

<sup>\*</sup>Value applying at rated voltage

#### 500 Hz

4000 Hz