WWW.MWFTR.COM/416F15.html Dr. Charles Kim

## EECE416 Microcomputer Fundamentals & Design

## **Computer Architecture**

Dr. Charles Kim Howard University

#### Ready to hack a better future?

The Hackster Hardware Weekend is a celebration of makers, open source hardware and the Hackster community across America. From Seattle to NYC and everything in between, we are hitting the road driving an original DeLorean DMC 12 to run the coolest Hackathon & Meetup series of the year, with loads of hardware kits, amazing speakers, software freebies and great people. Our goal is simple: educate, connect and help people invent and create the seeds of a better future.

What will you build with the DeLorean? Share your ideas on the DeLorean projects page.

#### Schedule

#### Day 1

#### Day 2

| 10:00 am | Check-in and breakfast    | 9:00 am  | Work on your hacks and get breakfast    |

|----------|---------------------------|----------|-----------------------------------------|

| 11:00 am | Kickoff                   | 12:30 pm | Lunch break with industry speaker       |

| 11:30 am | Training workshops        | 4:00 pm  | Upload your hacks to Hackster           |

| 12:30 pm | Lunch served              | 5:30 pm  | Demo your hacks!                        |

| 1:00 pm  | Start hacking             | 6:30 pm  | Dinner served while judges deliberate   |

| 8:00 pm  | Dinner served             | 7:00 pm  | Winners announced, prizes awarded       |

| 12:00 am | Go home and get some rest | 8:00 pm  | Day two ends, thanks for participating! |

5404 Wisconsin Ave, Suite 700 (Microsoft) Chevy Chase Chevy Chase, MD 20815-3522

Saturday, September 19, 2015 at 10:00 AM - Sunday, September 20, 2015 at 8:00 PM (EDT)

#### When & Where

## "Computer Architecture"

#### **#** Computer Architecture

- Art of selecting and interconnecting hardware components to create functional unit (or computer)

- $\triangle$  2 points of view

#### **⊠Instruction Set architecture (ISA)**:

- the code that a CPU reads and acts upon. It is the machine language (or assembly language), including the instruction set, word size, memory address modes, processor registers, and address and data formats

- Interface between H/W and S/W

- programmers' point of view

#### **Microarchitecture** (or computer organization):

- describes the data paths, data processing elements and data storage elements, size of cache, and describes how they should implement the ISA

- Optimization

- Power Management

- system designers' point of view.

#### Analogy:

⊠ House (rooms) – views of builders and residents

⊠Car – views of manufacturers (or mechanics) and drivers

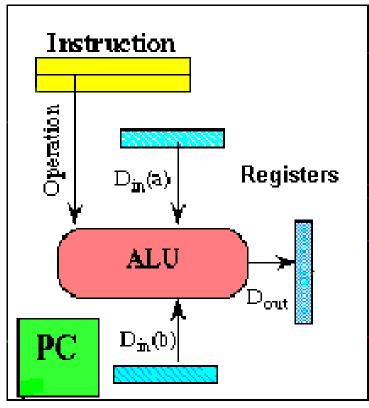

## **Micro-Architecture**

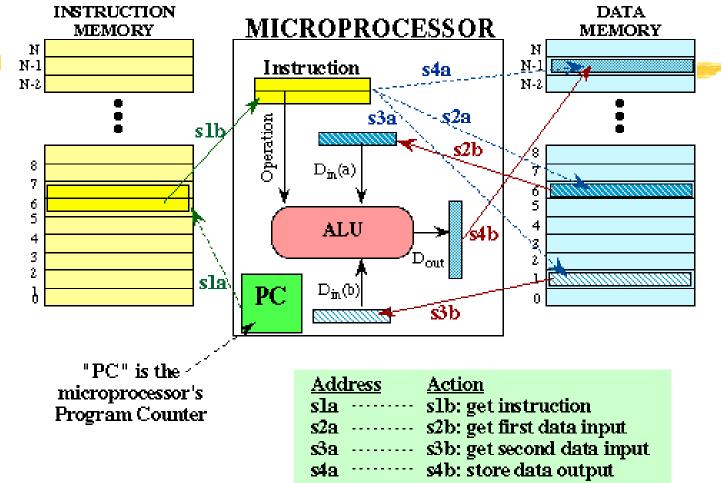

#### **K** Computer System

CPU (with PC, Register, SR) + Memory

#### **Hicro-Architecture:**

- "conceptual design and fundamental operational structure of a computer system"

- "blueprint and functional description of requirements and design implementations of a computer"

- focusing on the way the CPU performs and accesses memory.

#### Microprocessor

## **Micro-Architecture**

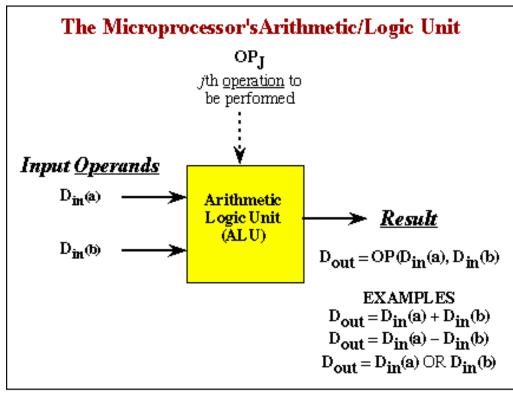

## ALU (Arithmetic Logic Unit)

- Fundamental building block of CPU

- Binary Full Adder

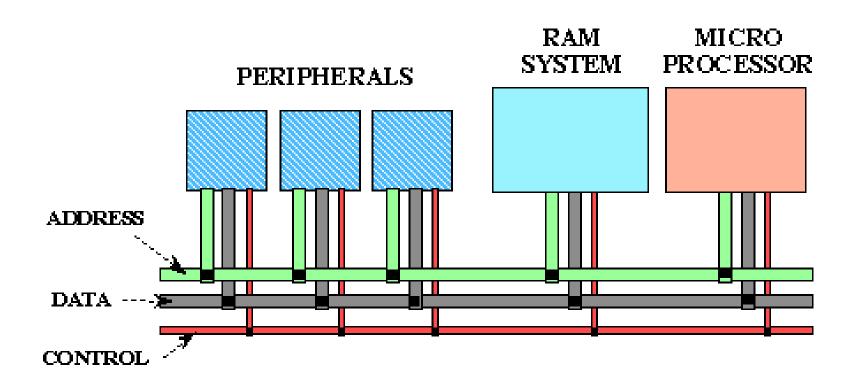

# **Microprocessor Bus**

7

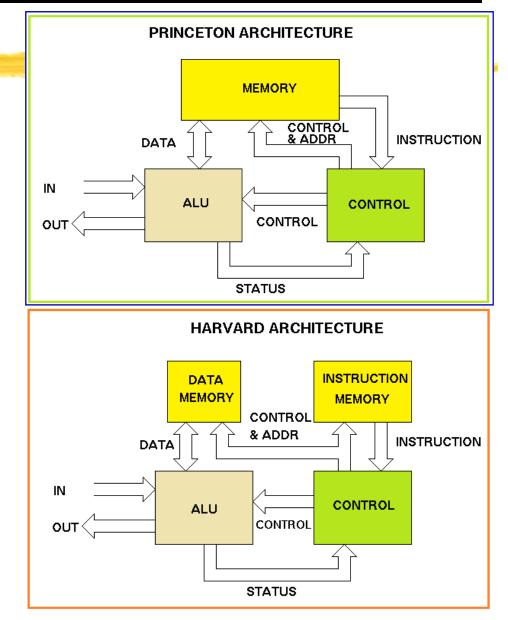

## Architecture by CPU+MEM organization

- Princeton (or von Neumann) Architecture

MEM contains both Instruction and Data

- ✓ Von Neumann Bottleneck CPU <→ Memory</p>

- Cache

- Harvard Architecture

- Data MEM and Instruction MEM

- Higher Performance via Pipeline

- Better for DSP

- Higher MEM Bandwidth

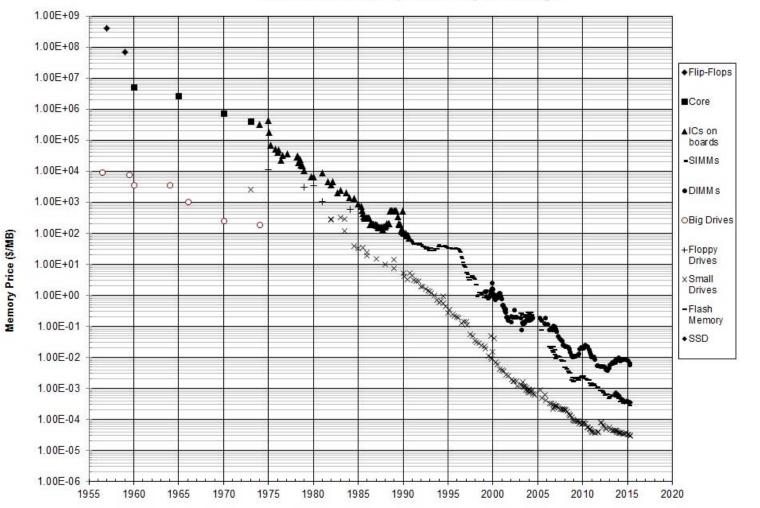

## **Memory Price**

🗲 ) 🛞 www.jcmit.com/mem2015.htm

VC Q Search

#### Graph of Memory Prices Decreasing with Time (1957-2015)

#### Historical Cost of Computer Memory and Storage

----

## **Memory Price**

VC Q Search

#### Chart of Memory Price Through Time Download Excel Spreadsheet of Memory Data

Home

| 10 March 10          | \$/Mbyte<br>(Y)       | Date                | Ref:                        | Page | Company         | Size    | Cost    | Speed | Memory Type                       |

|----------------------|-----------------------|---------------------|-----------------------------|------|-----------------|---------|---------|-------|-----------------------------------|

|                      |                       |                     |                             |      |                 | KByte   | US \$   | nsec  |                                   |

| 1957.00              | 411,041,792           | 1957                | Phister 366                 |      | C.C.C.          | 0.00098 | 392.00  | 10000 | transistor Flip-Flop              |

| 1959.00              | 67,947,725            | 1959                | Phister 366                 |      | E.E.Co.         | 0.00098 | 64.80   | 10000 | vacuum tube Flip-Flop             |

| 1960.00              | 5,242,880             | 1960                | Phister 367                 |      | IBM             | 0.00098 | 5.00    | 11500 | IBM 1401 core memory              |

| 1965.00 2            | 2,642,412             | 1965                | Phister 367                 |      | IBM             | 0.00098 | 2.52    | 2000  | IBM 360/30 core memory            |

| 1970.00              | 734,003               | 1970                | Phister 367                 |      | IBM             | 0.00098 | 0.70    | 770   | IBM 370/135 core memory           |

| 1973.00              | 399,360               | 1973 Jai            | n PDP8/e User<br>Price List |      | DEC             | 12      | 4680.00 | )     | Core memory 8KwordX12 bit         |

| 1974.00              | 314,573               | 1974                | Phister 367                 |      | IBM             | 0.00098 | 0.30    | 800   | IC Memory for IBM 370/125         |

| 1975.00 <sup>4</sup> | 421,888               | 1975 Jai            | n Radio-<br>Electronics     |      | MITS            | 0.25    | 103.00  | 1000  | Altair 8800 256 Byte Static Board |

| 1975.08              | 180,224               | 1975 Fe             | b                           |      | MITS            | 1       | 176.00  |       | Altair 1K Static Board            |

| 1975.25              | 67,584                | 1975 Ar             | or                          |      | MITS            | 4       | 264.00  |       | Altair 4K DRAM Board              |

| 1975.75              | 49,920                | 1975 Oc             | :t                          |      | MITS            | 4       | 195.00  |       | Altair 4K Static(2102) RAM Board  |

| 1976.00 4            | 40,704                | 1976 Jan            | n                           |      | MITS            | 4       | 159.00  |       | Altair 4K Static(2102) RAM Board  |

| 1976.17 4            | 48,960                | 1976 M              | ar                          |      | MITS            | 16      | 765.00  |       | Altair 16K Static RAM Board       |

| 1976.42              | 23,040                | 1976 Ju             | n                           |      | SD Sales        | 4       | 90.00   |       | SD Sales 4K Static Board          |

| 1976.58              | 32,000                | 1976 Au             | ıg                          |      |                 | 8       | 250.00  |       | 8K Static RAM Board               |

| 1977.08              | 36,800                | 1977 Fe             | b                           |      | TDL             | 16      | 575.00  |       | S-100 16K                         |

| 1978.17 2            | 28,000                | 1978 M              | ar                          |      |                 | 64      | 1750.00 | )     | S-100 64K                         |

| 1978.25 2            | 29,440                | 1978 A <sub>f</sub> | or                          |      |                 | 16      | 460.00  |       |                                   |

| 1978.33              | 19,200                | 1978 M              | ay                          |      |                 | 16      | 300.00  |       |                                   |

| 1978.50 2            | 24,000                | 1978 Ju             | <u> </u>                    |      | Extensis        | 64      | 1500.00 | )     |                                   |

| 1978.58              | 16 <mark>,00</mark> 0 | 1978 Au             | ıg                          |      |                 | 8       | 125.00  |       |                                   |

| 1978.75              | 15,200                | 1978 Oc             | t                           |      |                 | 32      | 475.00  |       |                                   |

| 1979.00              | 10,528                | 1979 Jan            | n Interface Age             | 124  |                 | 32      | 329.00  |       |                                   |

| 1979.75              | 6,704                 | 1979 Oc             | :t                          |      | SD Sales - Jade | 64      | 419.00  |       | S-100, SD Sales/Jade 64K Kit      |

| 1980.00              | 6,480                 | 1980 Jan            | n Interface Age             | 121  |                 | 64      | 405.00  |       |                                   |

# "Pipeline"?

## **#Instruction Pipeline**

An **instruction pipeline** is a technique used in the design of **computers** to increase their instruction throughput (the number of instructions that can be executed in a unit of time). Pipelining does not reduce the time to complete an instruction, but increases instruction throughput by performing multiple operations in parallel.

The term pipeline is an analogy to the fact that there is fluid in each link of a pipeline, as each part of the processor is occupied with work.

| Instr. No.     |   | Pipeline Stage |    |     |     |     |     |

|----------------|---|----------------|----|-----|-----|-----|-----|

| 1              | F | ID             | ΕX | MEM | WB  |     |     |

| 2              |   | IF             | ID | ΕX  | мем | WB  |     |

| 3              |   |                | IF | ID  | ΕX  | мем | WB  |

| 4              |   |                |    | IF  | ID  | ΕX  | MEM |

| 5              |   |                |    |     | IF  | ID  | EX  |

| Clock<br>Cycle | 1 | 2              | 3  | 4   | 5   | 6   | 7   |

Basic five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back). In the fourth clock cycle (the green column), the earliest instruction is in MEM stage, and the latest instruction has not yet entered the pipeline.

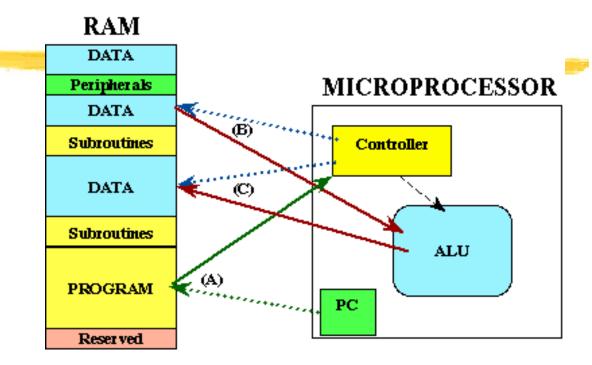

## **Princeton Architecture**

1.Step (A): The

address for the instruction to be next executed is read into

2. **Step (B):** The controller "decodes" the instruction

3.**Step (C)**: Following completion of the instruction, the controller provides the address, to the memory unit, at which the data result generated by the operation will be stored.

•CPU can be either reading an instruction or reading/writing data from/to the memory.

•Both cannot occur at the same time since the instructions and the data use the same bus system

## Harvard Architecture

- 1. CPU can both read an instruction and perform a data memory access at the same time.

- 2. Faster for a given circuit complexity because instruction fetches and data access do not contend for a single memory pathway.

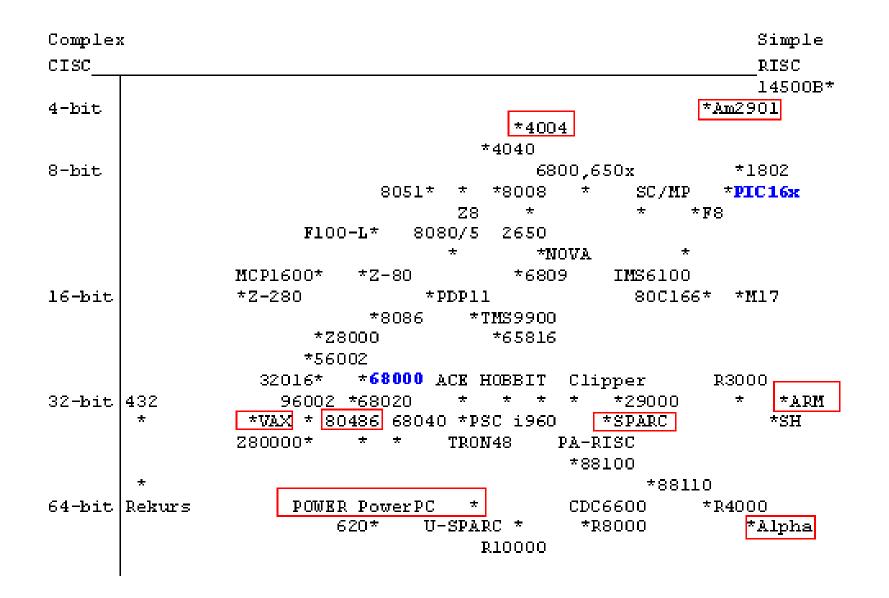

## Architecture by Instructions and Executions

- #CISC (Complex Instruction Set Computer)

- Variety of instructions for complex tasks directly to hardware

- Easy to translate high-level language to assembly

- △Complex Hardware

- Instructions of varying length

- #RISC (Reduced Instruction Set Computer)

- ⊡ Fewer and simpler instructions

- Each instruction takes the same amount of time

- △Less complex hardware

- ☐ High performance microprocessors

- Pipelined instruction execution (several instructions are executed in parallel)

## CISC

#Architecture of prior to mid-1980's

IBM390, Motorola 680x0, Intel80x86

#Basic Fetch-Execute sequence to support a large number of complex instructions

#Complex decoding procedures

#Complex control unit

#One instruction achieves a complex task

# RISC

**#**Favorable changes for RISC

- Caches to speed instruction fetches

- □ Dramatic memory size increases/cost decreases

- ⊡Better *pipelining*

- Advanced optimizing compilers

- Characteristics of RISC

- Instructions are of a uniform length

- Increased number of registers to hold frequently used variables (16 - 64 Registers)

- Central to High Performance Computing

## **Processor Classification**

-

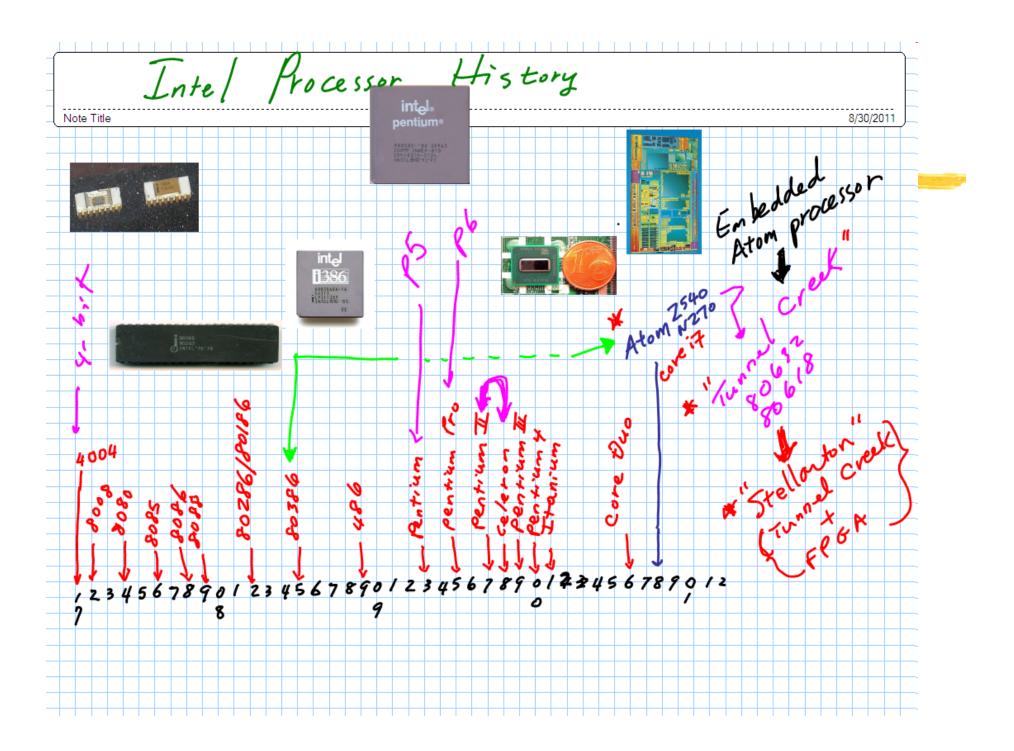

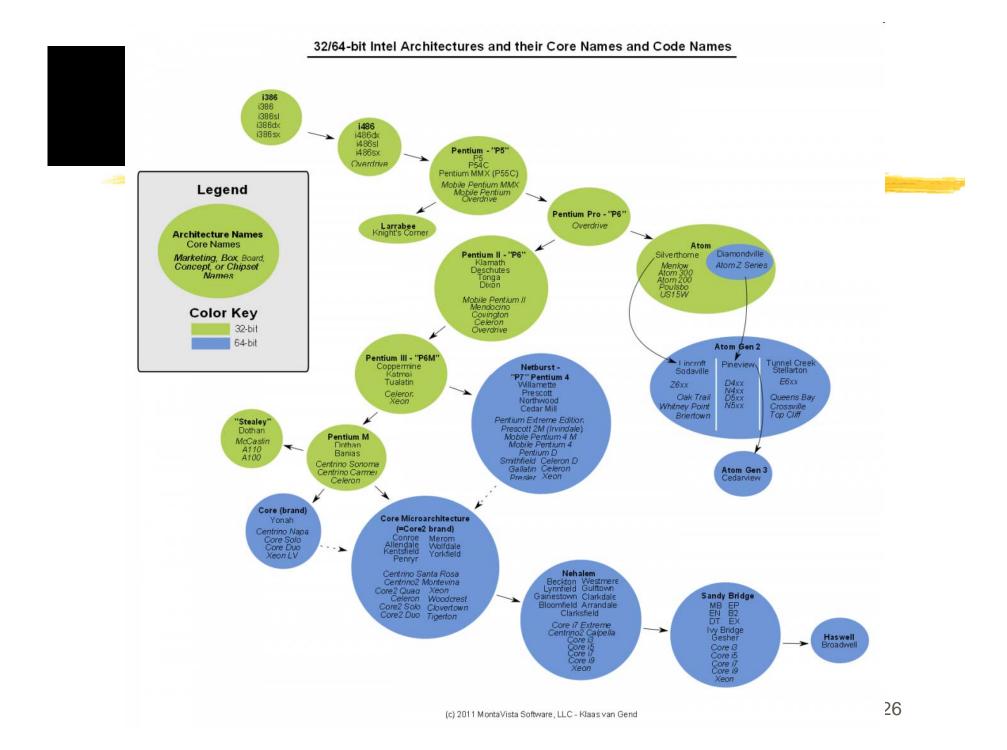

## Intel inside?

## **Kext PCs or Mobile Computing**

Devices

Smart phones

Apple Processors

ARMs

Qualcomm

Mobile Devices – Smartphones, MP3, Digicam (on ARM)

Run on Intel's x86? --- Intel's wish; what happened to Lumina?

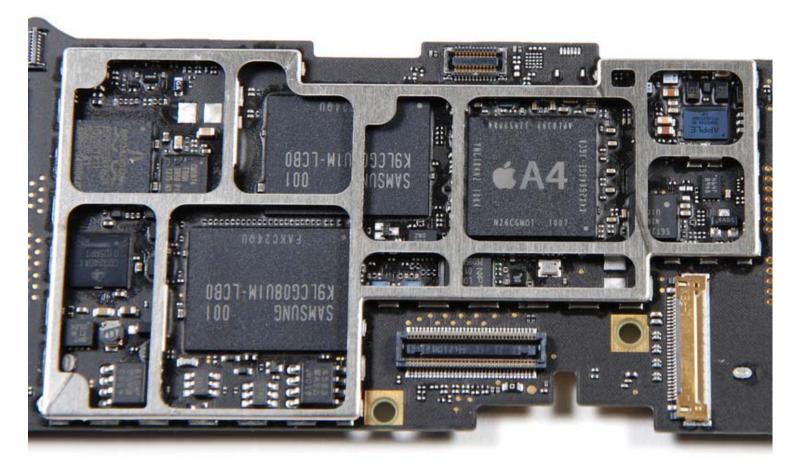

# What's inside?

## HiPhone: 1GHz-A4 microprocessor, 256MB Samsung RAM,

# What's inside?

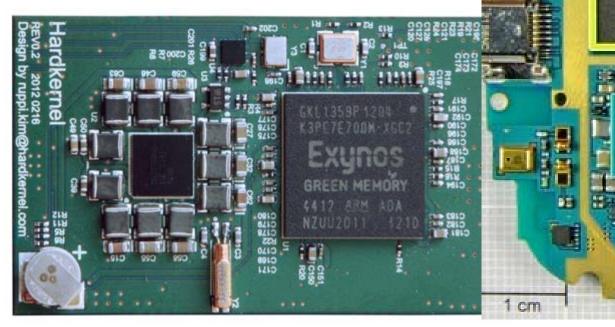

#### Samsung Galaxy

- Samsung Exynos quad-core A9 processor

- ☐ 1GB Memory

- ☐ Intel Wireless processor

- Broadcom Global Navigation Satellite System receiver

# What's Inside?

## **HTC**

# What's inside?

## **XNokia Lumina**

## △1.4GHz Qualcomm CPU, 512MB RAM, 16GB Storage,

💭 Təshikəpublis.

## INTEL VS. ARM ("Advanced RISC Machine")

ARMs

- No chip hardware license only (powerful and variety of licensees) → cell phones etc

- SoC device (CPU + I/O + Peripherals + Memory + etc)

# INTEL

- Does not want to License x86 (Lesson from AMD)

- △New approach for SoC: Atom based X86 SoC

- **Recent Stride with "Intel Atom Inside"**

- Main processor for Laptops and Netbooks and Tablets

- Motorola Phones: Razr

Intel Atom

| (inte<br>Ator | n <sup>w</sup> inside <sup>w</sup> |

|---------------|------------------------------------|

| duced         | 2008–present                       |

| nmon          | Intel                              |

| nufacturer(s) |                                    |

| CPU clock     | 800 MHz to 2 GHz                   |

Proc

| Common<br>manufacturer(s) | Intel                                    |

|---------------------------|------------------------------------------|

| Max. CPU clock            | 800 MHz to 2 GHz                         |

| FSB speeds                | 400 MHz to 667 MHz                       |

| Min. feature size         | 45nm                                     |

| Instruction set           | x86, x86-64 (not for the N and Z series) |

| Cores                     | 1,2                                      |

| Package(s)                | 441-ball µFCBGA                          |

| Core name(s)              | Silverthorne<br>Diamondville             |

# **Processor Performance**

Processor Performance Over Time and Other Key Features of the Intel Architecture

| Intel<br>Processor | Date of<br>Product<br>Intro-<br>duction | Perfor-<br>mance<br>in<br>MIPs <sup>1</sup> | Max. CPU<br>Frequency<br>at Intro-<br>duction | No. of<br>Transis<br>-tors<br>on the<br>Die | Main<br>CPU<br>Register<br>Size <sup>2</sup> | Extern.<br>Data<br>Bus<br><b>S</b> ize <sup>2</sup> | Max.<br>Extern.<br>Addr.<br>Space |

|--------------------|-----------------------------------------|---------------------------------------------|-----------------------------------------------|---------------------------------------------|----------------------------------------------|-----------------------------------------------------|-----------------------------------|

| 8086               | 1978                                    | 0.8                                         | 8 MHz                                         | 29 K                                        | 16                                           | 16                                                  | 1 MB                              |

| Intel 286          | 1982                                    | 2.7                                         | 12.5 MHz                                      | 134 K                                       | 16                                           | 16                                                  | 16 MB                             |

| Intel386™<br>DX    | 1985                                    | 6.0                                         | 20 MHz                                        | 275 K                                       | 32                                           | 32                                                  | 4 GB                              |

| Intel486™<br>DX    | 1989                                    | 20                                          | 25 MHz                                        | 1.2 M                                       | 32                                           | 32                                                  | 4 GB                              |

| Pentium®           | 1993                                    | 100                                         | 60 MHz                                        | 3.1 M                                       | 32                                           | 64                                                  | 4 GB                              |

| Pentium Pro        | 1995                                    | 440                                         | 200 MHz                                       | 5.5 M                                       | 32                                           | 64                                                  | 64 GB                             |

25

# Intel 805xx product codes

Intel discontinued the use of part numbers such as 80486 in the marketing of mainstream x86-architecture microprocessors with the introduction of the Pentium brand in 1993. However, numerical codes, in the 805xx range, continued to be assigned to these processors for internal and part numbering uses. The following is a list of such product codes in numerical order:

| Product<br>code | Marketing name(s)                      | Codename(s)                     |

|-----------------|----------------------------------------|---------------------------------|

| 80500           | Pentium                                | P5 (A-step)                     |

| 80501           | Pentium                                | P5                              |

| 80502           | Pentium                                | P54C, P54CS                     |

| 80503           | Pentium with MMX Technology            | P55C, Tillamook                 |

| 80521           | Pentium Pro                            | P6                              |

| 80522           | Pentium II                             | Klamath                         |

| 80523           | Pentium II, Celeron, Pentium II Xeon   | Deschutes, Covington, Drake     |

| 80524           | Pentium II, Celeron                    | Dixon, Mendocino                |

| 80525           | Pentium III, Pentium III Xeon          | Katmai, Tanner                  |

| 80526           | Pentium III, Celeron, Pentium III Xeon | Coppermine, Cascades            |

| 80528           | Pentium 4, Xeon                        | Willamette (Socket 423), Foster |

| 80529           | cancelled                              | Timna                           |

| 80530           | Pentium III, Celeron                   | Tualatin                        |

# Intel 805XX Product Codes

| 80531 | Pentium 4, Celeron                     | Willamette (Socket 478)                                        |

|-------|----------------------------------------|----------------------------------------------------------------|

| 80532 | Pentium 4, Celeron, Xeon               | Northwood, Prestonia, Gallatin                                 |

| 80533 | Pentium III                            | Coppermine (cD0-step)                                          |

| 80534 | Pentium 4 SFF                          | Northwood (small form factor)                                  |

| 80535 | Pentium M, Celeron M 310-340           | Banias                                                         |

| 80536 | Pentium M, Celeron M 350-390           | Dothan                                                         |

| 80537 | Core 2 Duo T5xxx, T7xxx, Celeron M 5xx | Merom                                                          |

| 80538 | Core Solo, Celeron M 4xx               | Yonah                                                          |

| 80539 | Core Duo, Pentium Dual-Core T-series   | Yonah                                                          |

| 80541 | Itanium                                | Merced                                                         |

| 80542 | Itanium 2                              | McKinley                                                       |

| 80543 | Itanium 2                              | Madison                                                        |

| 80546 | Pentium 4, Celeron D, Xeon             | Prescott (Socket 478), Nocona,<br>Irwindale, Cranford, Potomac |

| 80547 | Pentium 4, Celeron D                   | Prescott (LGA 775)                                             |

| 80548 | canceled                               | Tejas and Jayhawk                                              |

| 80549 | Itanium 2 90xx                         | Montecito                                                      |

# Intel 805XX Product Codes

| 80550               | Dual-Core Xeon 71xx                                                      | Tulsa                   |

|---------------------|--------------------------------------------------------------------------|-------------------------|

| 80551               | Pentium D, Pentium EE, Dual-Core Xeon                                    | Smithfield, Paxville DP |

| 80552               | Pentium 4, Celeron D                                                     | Cedar Mill              |

| 80553               | Pentium D, Pentium EE                                                    | Presler                 |

| 80554               | Celeron 800/900/1000 ULV                                                 | Shelton                 |

| 80555               | Dual-Core Xeon 50xx                                                      | Dempsey                 |

| 80556               | Dual-Core Xeon 51xx                                                      | Woodcrest               |

| 80557               | Core 2 Duo E4xxx. E6xxx, Dual-Core Xeon 30xx,<br>Pentium Dual-Core E2xxx | Conroe                  |

| 80560               | Dual-Core Xeon 70xx                                                      | Paxville MP             |

| 80562               | Core 2 Quad, Core 2 Extreme QX6xxx, Quad-Core<br>Xeon 32xx               | Kentsfield              |

| 80563               | Quad-Core Xeon 53xx                                                      | Clovertown              |

| 80564               | Xeon 7200                                                                | Tigerton-DC             |

| 80565               | Xeon 7300                                                                | Tigerton                |

| 80566               | Atom Z5xx                                                                | Silverthorne            |

| 8 <mark>0567</mark> | Itanium 91xx                                                             | Montvale                |

| 80569               | Core 2 Quad Q9xxx, Core 2 Extreme QX9xxx, Xeon<br>33xx                   | Yorkfield               |

# Intel 805XX Product Codes

| 80570 | Core 2 Duo E8xxx, Xeon 31xx                                                           | Wolfdale        |

|-------|---------------------------------------------------------------------------------------|-----------------|

| 80571 | Core 2 Duo E7xxx, Pentium Dual-Core E5xxx,<br>Pentium Dual-Core E2210                 | Wolfdale-3M     |

| 80573 | Xeon 5200                                                                             | Wolfdale-DP     |

| 80574 | Core 2 Extreme QX9775, Xeon 5400                                                      | Harpertown      |

| 80576 | Core 2 Duo P7xxx, T8xxx, P8xxx, T9xxx, P9xxx,<br>SL9xxx, SP9xxx, Core 2 Extreme X9xxx | Penryn          |

| 80577 | Core 2 Duo P7xxx, P8xxx, SU9xxx, T6xxx, T8xxx                                         | Penryn-3M       |

| 80578 | LE80578                                                                               | Vermilion Range |

| 80579 | EP80579                                                                               | Tolapai         |

| 80580 | Core 2 Quad Q8xxx, Q9xxx, Xeon 33xx                                                   | Yorkfield-6M    |

| 80581 | Core 2 Quad Q9xxx                                                                     | Penryn-QC       |

| 80582 | Xeon 74xx                                                                             | Dunnington      |

| 80583 | Xeon 74xx                                                                             | Dunnington-QC   |

| 80584 | Xeon X33x3 LV                                                                         | Yorkfield CL    |

| 80585 | Core 2 Solo SU3xxx, Celeron 7xx, 9xx                                                  | Penryn-L        |

| 80586 | Atom 2xx, N2xx                                                                        | Diamondville    |

| 80587 | Atom 3xx                                                                              | Diamondville DC |

| 80588 | Xeon L3014, E3113                                                                     | Wolfdale-CL     |

# Intel 806XX Product Codes

#### Intel 806xx product codes

| Product<br>code | Marketing name(s)                                 | Codename(s) |

|-----------------|---------------------------------------------------|-------------|

| 80601           | Core i7, Xeon 35xx                                | Bloomfield  |

| 80602           | Xeon 55xx                                         | Gainestown  |

| 80603           | Itanium 93xx                                      | Tukwila     |

| 80604           | Xeon 65xx, Xeon 75xx                              | Beckton     |

| 80605           | Core i5-7xx, Core i7-8xx, Xeon 34xx               | Lynnfield   |

| 80606           | canceled                                          | Havendale   |

| 80607           | Core i7-7xx QM, Core i7-8xx QM, Core<br>i7-9xx XM | Clarksfield |

| 80608           | canceled                                          | Auburndale  |

| 80609           | Atom                                              | Lincroft    |

| 80610           | Atom N400, D400, D500                             | Pineview    |

# Intel 806XX Product Codes

| 80611 | canceled                                            | Larrabee                                                 |

|-------|-----------------------------------------------------|----------------------------------------------------------|

| 80612 | Xeon C35xx, Xeon C55xx                              | Jasper Forest                                            |

| 80613 | Core i7-9xxX, Xeon 36xx                             | Gulftown                                                 |

| 80614 | Xeon 56xx                                           | Westmere-EP                                              |

| 80615 | Xeon E7-28xx, Xeon E7-48xx                          | Westmere-EX                                              |

| 80616 | Pentium G6xxx, Core i3-5xx, Core i5-6xx             | Clarkdale                                                |

| 30617 | Core i5-5xx, Core i7-6xxM/UM/LM                     | Arrandale                                                |

| 30618 | Atom                                                | Tunnel Creek                                             |

| 30620 | Xeon                                                | Sandy Bridge-EP-8, Sandy Bridge-EP-4                     |

| 30621 | Xeon                                                | Sandy Bridge-EP-8, Sandy Bridge-EP-4                     |

| 80622 | Xeon                                                | Sandy Bridge-EP-8                                        |

| 80623 | Xeon E3-xxxx, Core i3/i5/i7-2xxx, Pentium<br>Gxxx   | Sandy Bridge-HE-4, Sandry Bridge-M-2                     |

| 30627 | Core i3/i5/i7-2xxxM,, Pentium Bxxx,<br>Celeron Bxxx | Sandy Bridge-HE-4, Sandy Bridge-H-2, Sandy<br>Bridge-M-2 |

| 30632 | Atom                                                | Tunnel Creek                                             |

| 30640 | Atom                                                | Penwell                                                  |

| 80641 | Atom                                                | Cedar View                                               |

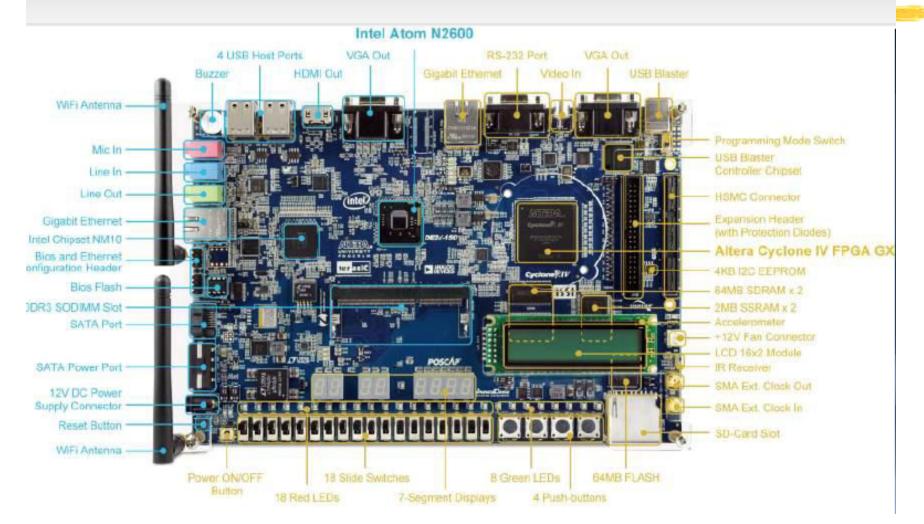

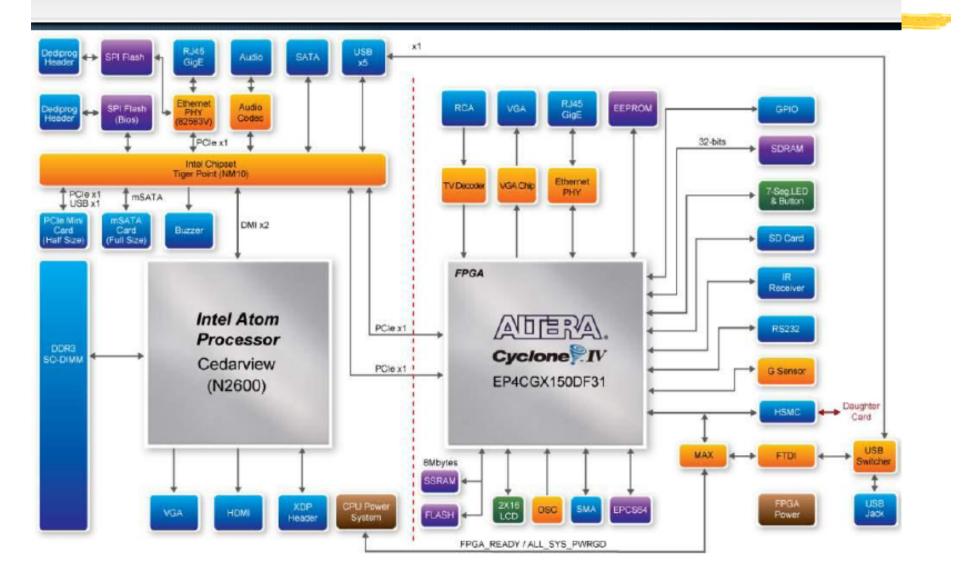

## **New Intel Atom DE2i-150 Board**

## DE2i-150 Kit Contents

# **DE2i-150 Kit**

## DE2i-150 Floorplan

# **DE2i-150 Kit**

## DE2i-150 Block Diagram

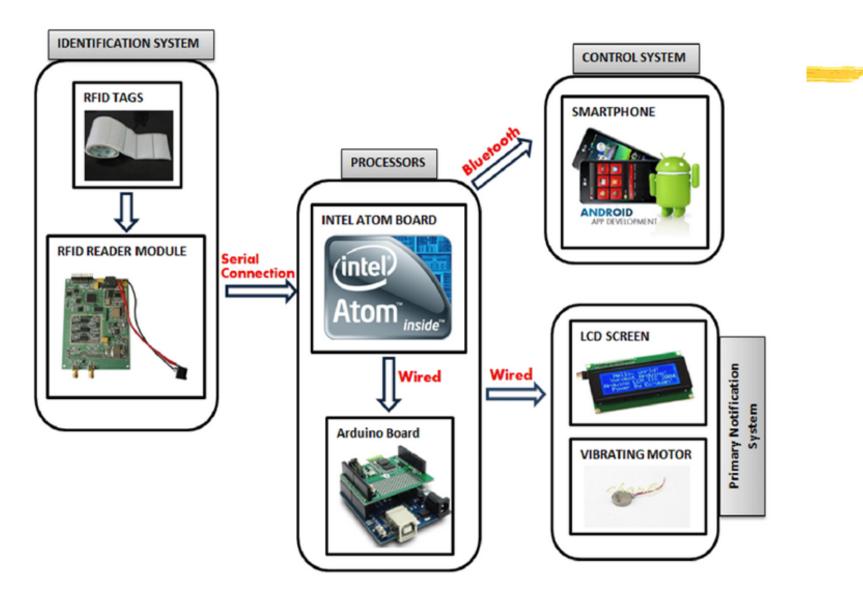

## What/How HU students did? An example

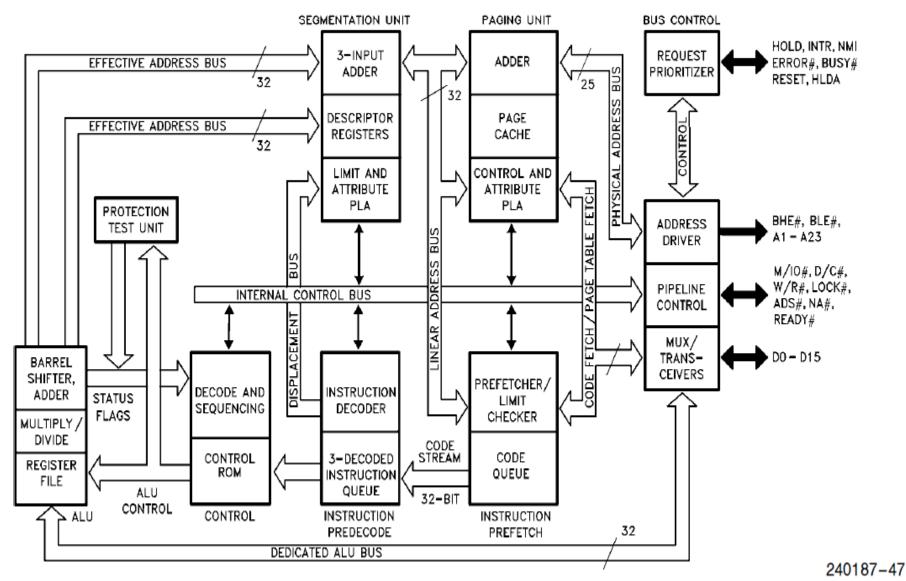

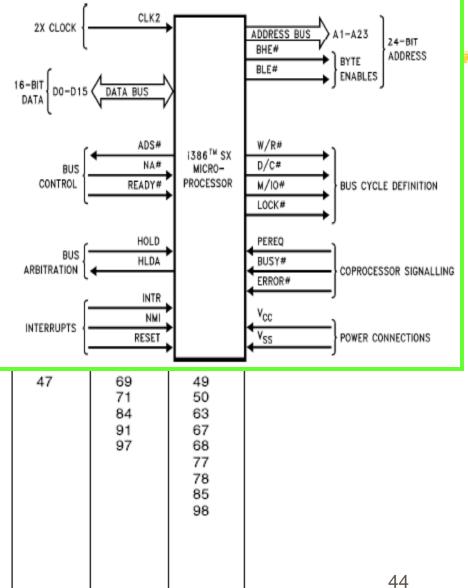

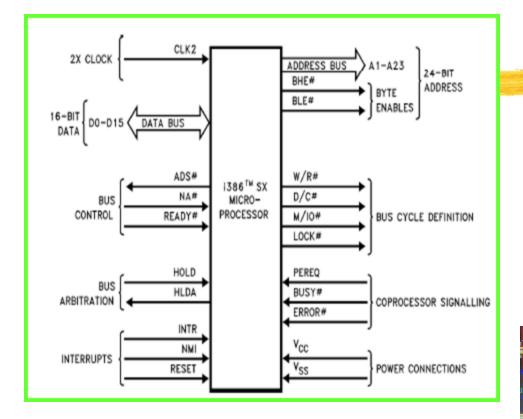

## Intel 386 - Datasheet

# intəl

#### Intel386<sup>™</sup> SX MICROPROCESSOR

24

- Full 32-Bit Internal Architecture

- 8-, 16-, 32-Bit Data Types

- 8 General Purpose 32-Bit Registers

- Runs Intel386<sup>TM</sup> Software in a Cost Effective 16-Bit Hardware Environment

- Runs Same Applications and O.S.'s as the Intel386™ DX Processor

- Object Code Compatible with 8086, 80186, 80286, and Intel386™ Processors

- High Performance 16-Bit Data Bus

- 16, 20, 25 and 33 MHz Clock

- Two-Clock Bus Cycles

- Address Pipelining Allows Use of Slower/Cheaper Memories

- Integrated Memory Management Unit

- Virtual Memory Support

- Optional On-Chip Paging

- 4 Levels of Hardware Enforced Protection

- MMU Fully Compatible with Those of the 80286 and Intel386 DX CPUs

- Virtual 8086 Mode Allows Execution of 8086 Software in a Protected and Paged System

- Large Uniform Address Space 16 Megabyte Physical

- 64 Terabyte Virtual

- 4 Gigabyte Maximum Segment Size 🦛 32

DIR

Ιь

- Numerics Support with the Intel387TM SX Math CoProcessor

- On-Chip Debugging Support Including Breakpoint Registers

- Complete System Development Support

- Software: C, PL/M, Assembler

- Debuggers: PMON-386 DX, ICE<sup>TM</sup>-386 SX

- High Speed CHMOS IV Technology

- Operating Frequency:

- Standard (Intel386 SX -33, -25, -20, -16) Min/Max Frequency (4/33, 4/25, 4/20, 4/16) MHz

- Low Power (Intel386 SX -33, -25, -20, -16, -12) Min/Max Frequency (2/33, 2/25, 2/20, 2/16, 2/12) MHz

- 100-Pin Plastic Quad Flatpack Package (See Packaging Outlines and Dimensions #231369)

## Intel 386 - Datasheet

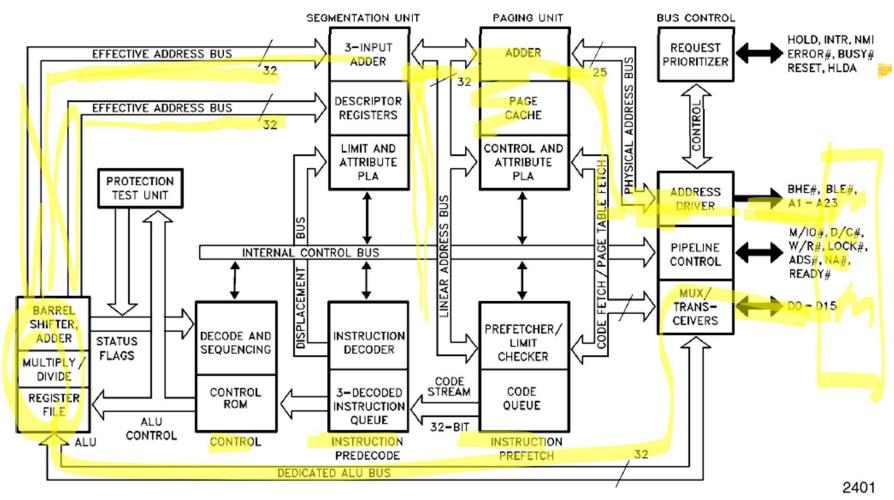

Intel386<sup>™</sup> SX Pipelined 32-Bit Microarchitecture

## Intel 386 - Brief

00 66 88

$\cap$

HLDA

HOLD

READY

000000

> A20

A18

A17

V<sub>CC</sub> V<sub>SS</sub> A15 A14 A13 V<sub>SS</sub> A12

A11 A10 A9 A8 V<sub>CC</sub> A7 A6 A5

> A4

53

5:

- 🔀 Address: A23- A1

- ☑ BLE# and BHE# ("Byte Enable")

- 🔀 Data: D15 D0

- ₭ Control

|                                                                                                                                                                                               |                                                       |                            |                                                                                                                                                             |                                                                                                           |                                                          |                                                                                | 12<br>13<br>14<br>15<br>16                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| Address                                                                                                                                                                                       |                                                       | Data                       | Control                                                                                                                                                     | I                                                                                                         | N/C                                                      | Vcc                                                                            | V <sub>SS</sub>                                                                                  |  |

| A2 5<br>A3 5<br>A4 5<br>A5 A6 5<br>A6 5<br>A7 5<br>A8 5<br>A9 5<br>A10 6<br>A11 6<br>A12 6<br>A12 6<br>A13 6<br>A14 6<br>A15 7<br>A16 7<br>A17 7<br>A18 7<br>A19 7<br>A19 7<br>A21 7<br>A22 7 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 87<br>2 86<br>8 83<br>8 82 | ADS#<br>BHE#<br>BLE#<br>BUSY#<br>CLK2<br>D/C#<br>ERROR#<br>FLT#<br>HLDA<br>HOLD<br>INTR<br>LOCK#<br>M/IO#<br>NA#<br>NMI<br>PEREQ<br>READY#<br>RESET<br>W/R# | 16<br>19<br>17<br>34<br>5<br>24<br>36<br>28<br>3<br>4<br>40<br>26<br>23<br>6<br>38<br>37<br>7<br>33<br>25 | 20<br>27<br>29<br>30<br>31<br>43<br>44<br>45<br>46<br>47 | 8<br>9<br>10<br>21<br>32<br>39<br>42<br>48<br>57<br>69<br>71<br>84<br>91<br>97 | 2<br>5<br>11<br>12<br>13<br>14<br>22<br>35<br>41<br>49<br>50<br>63<br>67<br>68<br>77<br>85<br>98 |  |

## **Review on Number Systems**

|     | Binary      | Hexadecimal | Decimal |  |

|-----|-------------|-------------|---------|--|

| 1.  | 100         |             |         |  |

| 2.  | 10101101    |             |         |  |

| 3.  | 1101110101  |             |         |  |

| 4.  | 11111011110 |             |         |  |

| 5.  | 1000000001  |             |         |  |

| 6.  |             | 8EF         |         |  |

| 7.  |             | 10          |         |  |

| 8.  |             | A52E        |         |  |

| 9.  |             | 70C         |         |  |

| 10. |             | 6BD3        |         |  |

| 11. |             |             | 100     |  |

| 12. |             |             | 527     |  |

| 13. |             |             | 4128    |  |

| 14. |             |             | 11947   |  |

| 15. |             |             | 59020   |  |

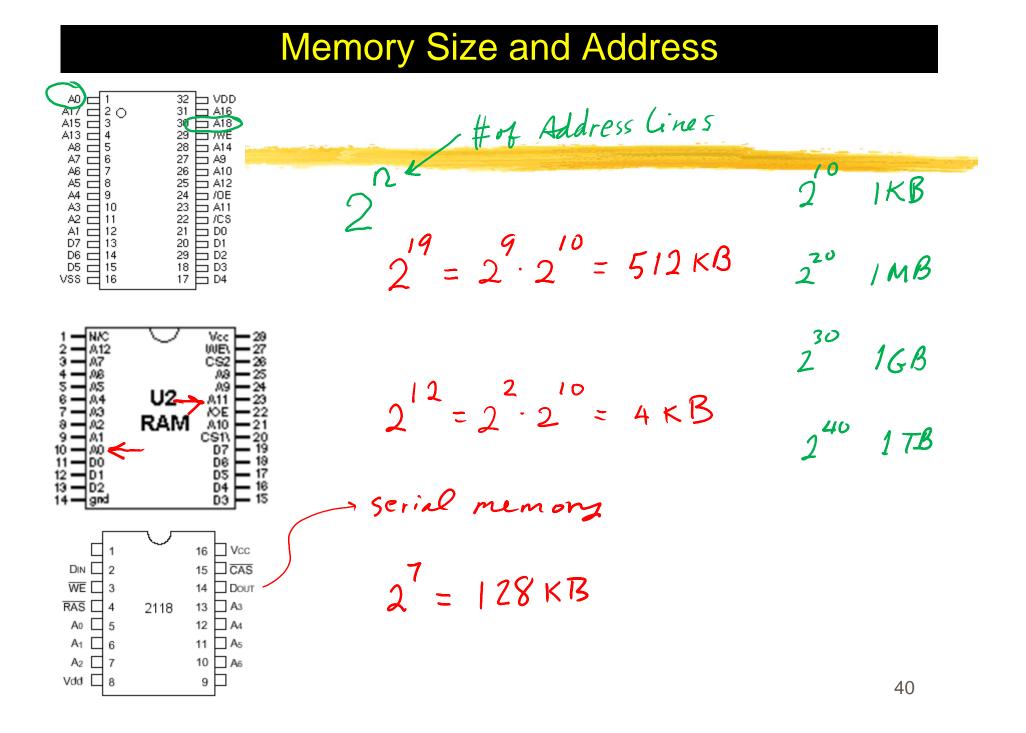

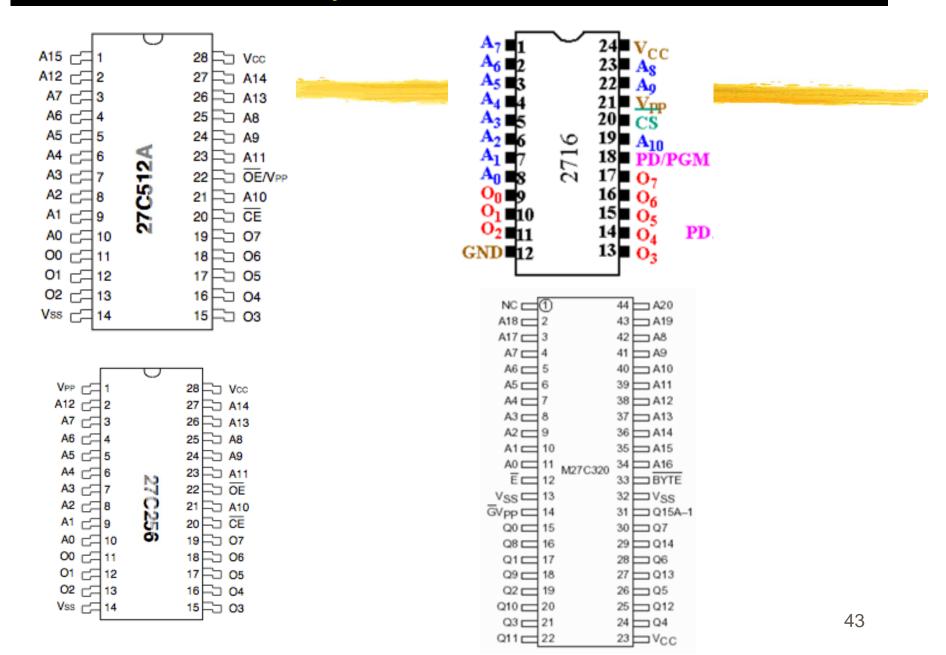

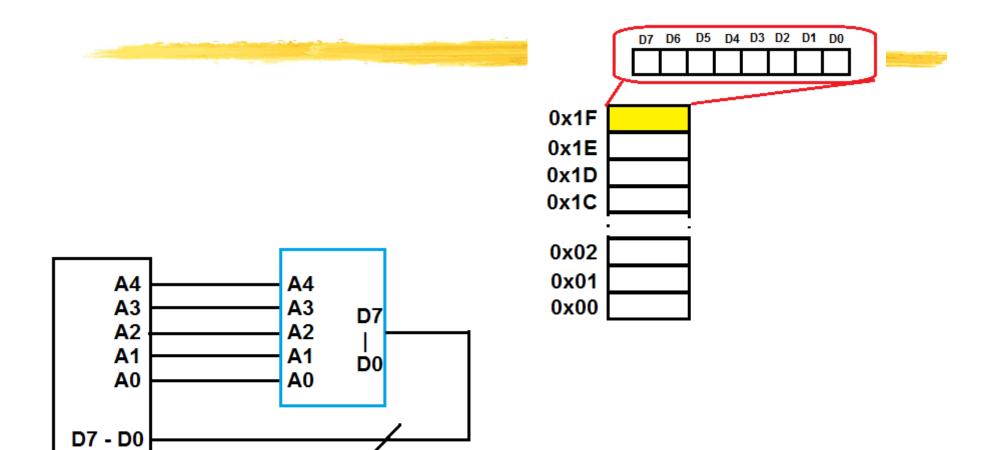

### Memory Size and Address 2

## Intel 386 - Brief

- Address: A23- A1 (where is A0?)BLE# and BHE# ("Byte Enable")

- 🔀 Data: D15 D0

- Control

|                                                                                                      |                                                                                  |                                                                                                                                              |                                                    |                                                                                           |                                                   | CONTROL | READY#                               | PROCESSOR                                          |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------|---------|--------------------------------------|----------------------------------------------------|

| Addr                                                                                                 | Address Data                                                                     |                                                                                                                                              | Contro                                             | I                                                                                         | ,                                                 |         |                                      |                                                    |

| A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8                                                         | 18<br>51<br>52<br>53<br>54<br>55<br>56<br>58<br>58                               | D <sub>0</sub><br>D <sub>1</sub><br>D <sub>2</sub><br>D <sub>3</sub><br>D <sub>4</sub><br>D <sub>5</sub><br>D <sub>6</sub><br>D <sub>7</sub> | 1<br>100<br>99<br>96<br>95<br>94<br>93<br>92<br>90 | ADS#<br>BHE#<br>BLE#<br>BUSY#<br>CLK2<br>D/C#<br>ERROR#<br>FLT#                           | 16<br>19<br>17<br>34<br>15<br>24<br>36<br>28<br>3 | BUS     | HOLD<br>HLDA<br>INTR<br>NMI<br>RESET |                                                    |

| A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>A16<br>A17<br>A18<br>A19<br>A20<br>A21<br>A22<br>A23 | 59<br>60<br>61<br>62<br>65<br>66<br>70<br>72<br>73<br>74<br>75<br>76<br>79<br>80 | D <sub>8</sub><br>D <sub>10</sub><br>D <sub>11</sub><br>D <sub>12</sub><br>D <sub>13</sub><br>D <sub>14</sub><br>D <sub>15</sub>             | 89<br>88<br>87<br>86<br>83<br>82<br>81             | HLDA<br>HOLD<br>INTR<br>LOCK#<br>M/IO#<br>NA#<br>NMI<br>PEREQ<br>READY #<br>RESET<br>W/R# | 4<br>40<br>26<br>38<br>37<br>7<br>33<br>25        | 47      | 69<br>71<br>84<br>91<br>97           | 49<br>50<br>63<br>67<br>68<br>77<br>78<br>85<br>98 |

### 386 Micro-Architecture

Intel386<sup>™</sup> SX Pipelined 32-Bit Microarchitecture

#### Connecting with Memory, I/O, and Peripherals

- Single Board Computers

- Processor Boards

- Kits

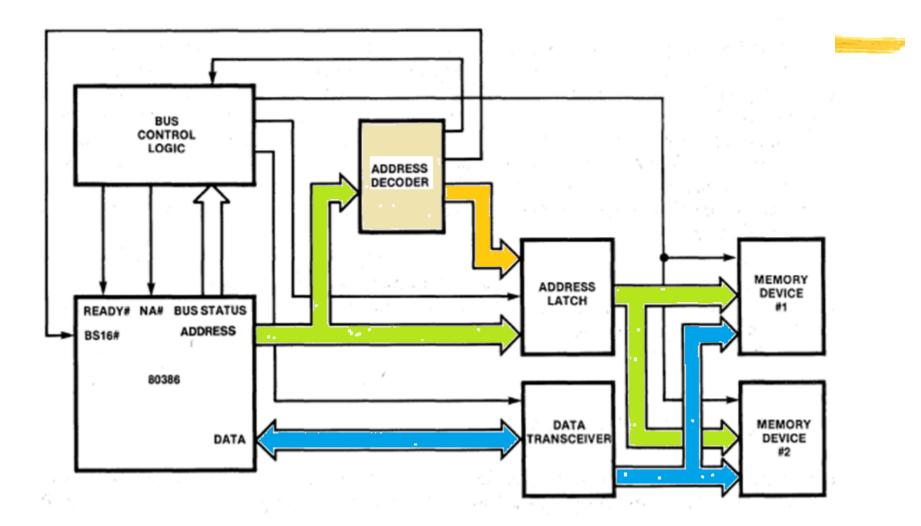

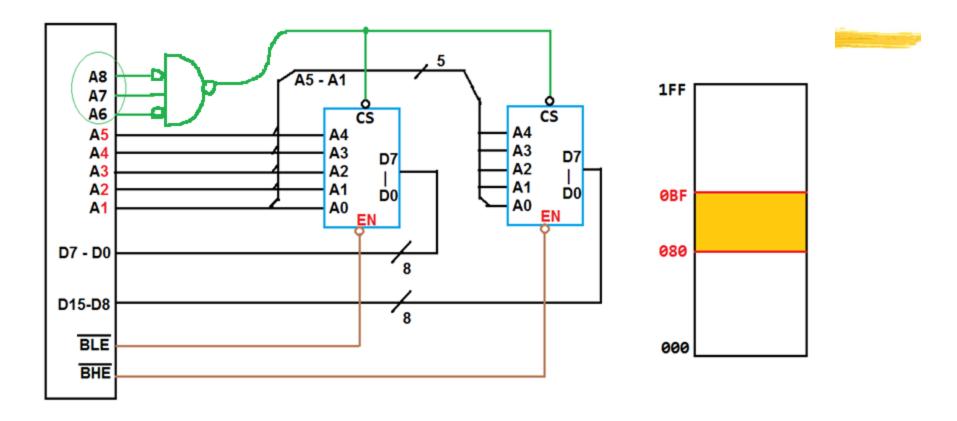

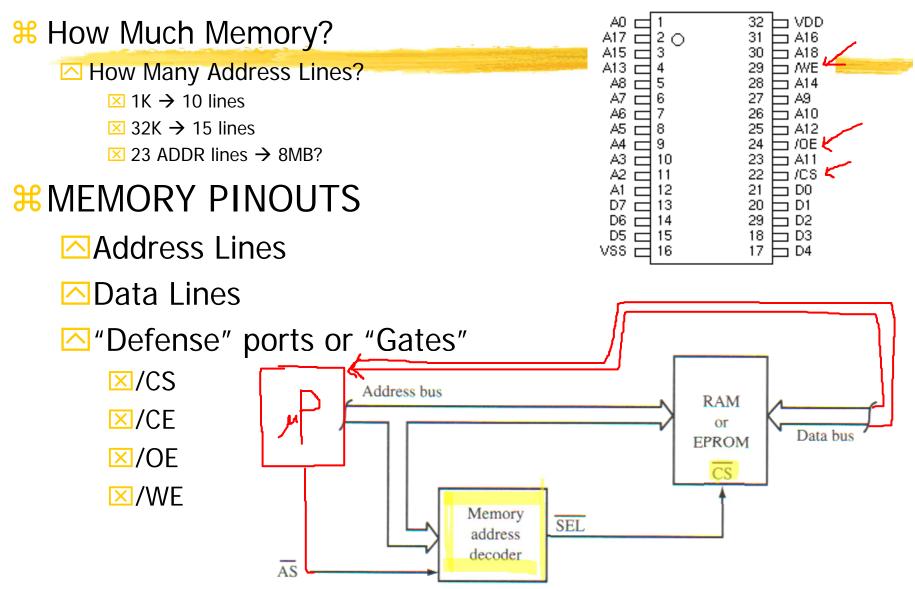

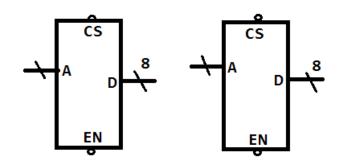

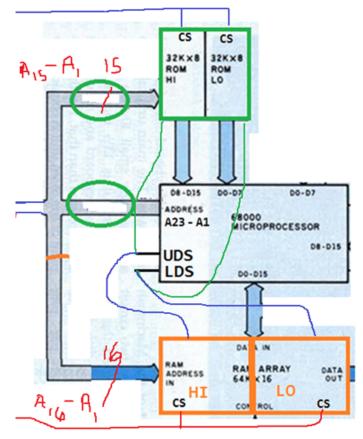

## **Memory Interface**

## **Memory Interface**

- Interface between a processor and a (pair) of memory (of smaller than the maximum memory space)

- ₩ Where do we place the memory in the memory space? → "MEMORY DECODING"

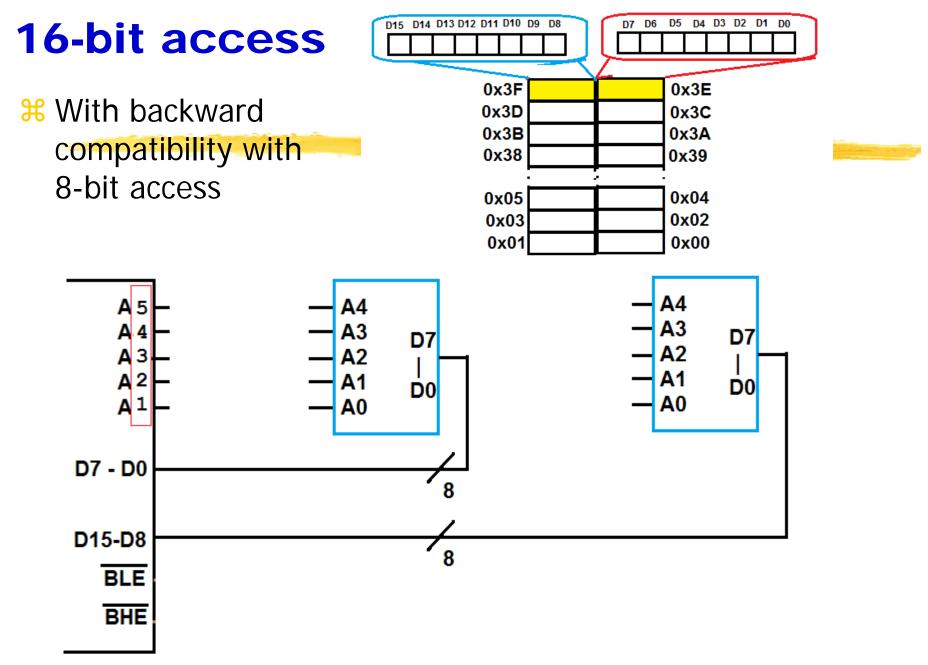

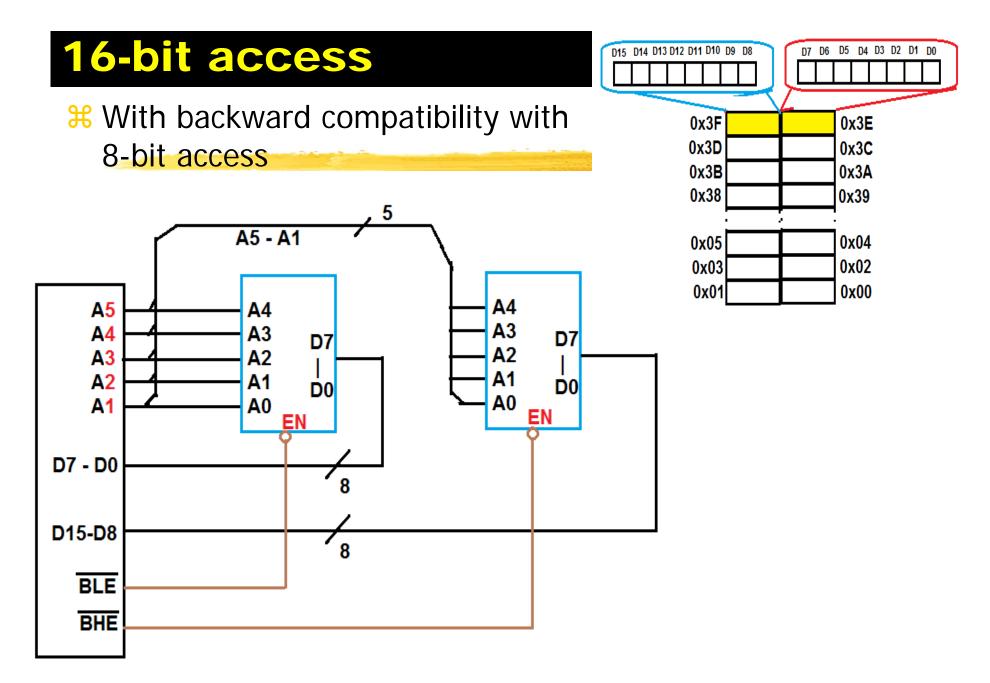

- How to access two MEM locations at the same time (for 16-bit Data bus)?

MEM --- Byte Access (8 bits)

UDS and LDS --- Motorola

BLE and BHE --- Intel

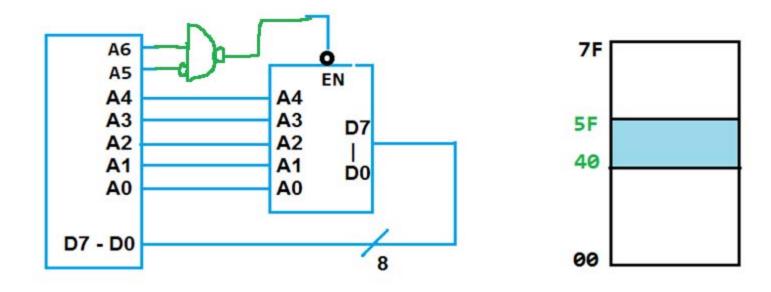

## 8-bit access

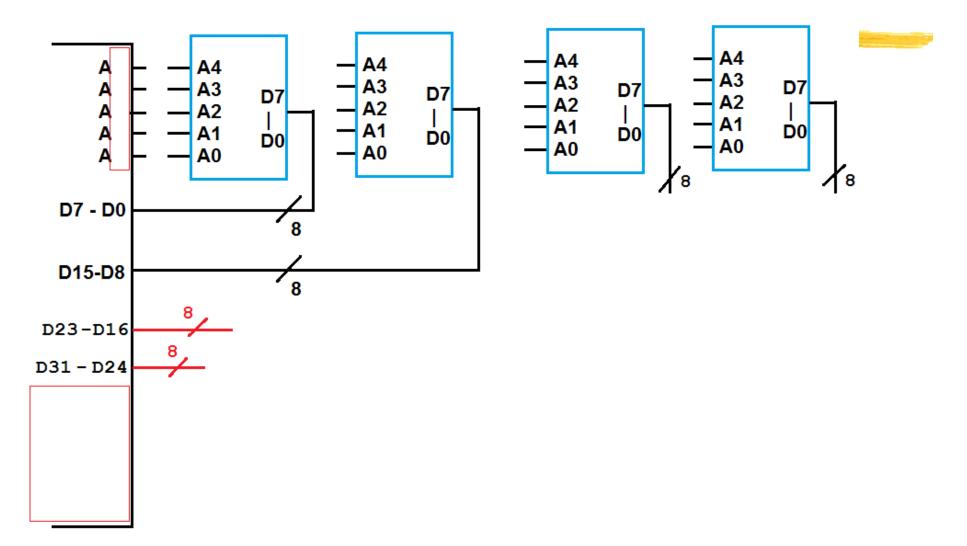

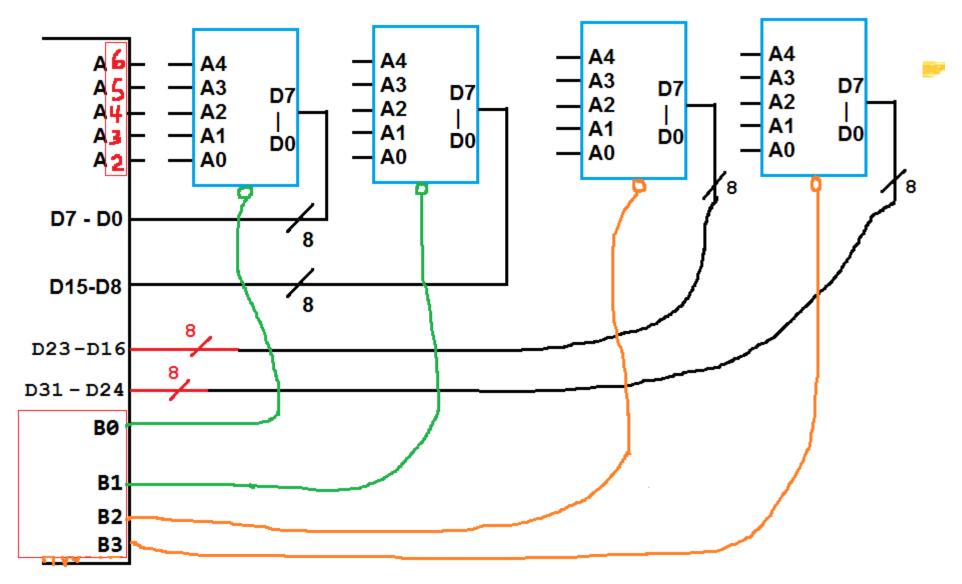

#### 32-bit access with backward compatibility?

#### 32-bit access with backward compatibility

## Memory Address 8

∺Address location (first and last addresses)?

## **Memory Address 8**

## Memory Address 8 ---?

Consign a Memory Decoder so that the 32Byte memory locates as depicted.

## Memory Address 8 ---?

Control Con

## Memory Address 16 – Address Space

## Memory Address 16

1C1

.

001

**1C0**

#### Memory Address 16 -- ?

**#** Design a memory decoder for the depicted address segment.

#### Memory Address 16 -- ?

**#** Design a memory decoder for the depicted address segment.

## Memory Address Decoding

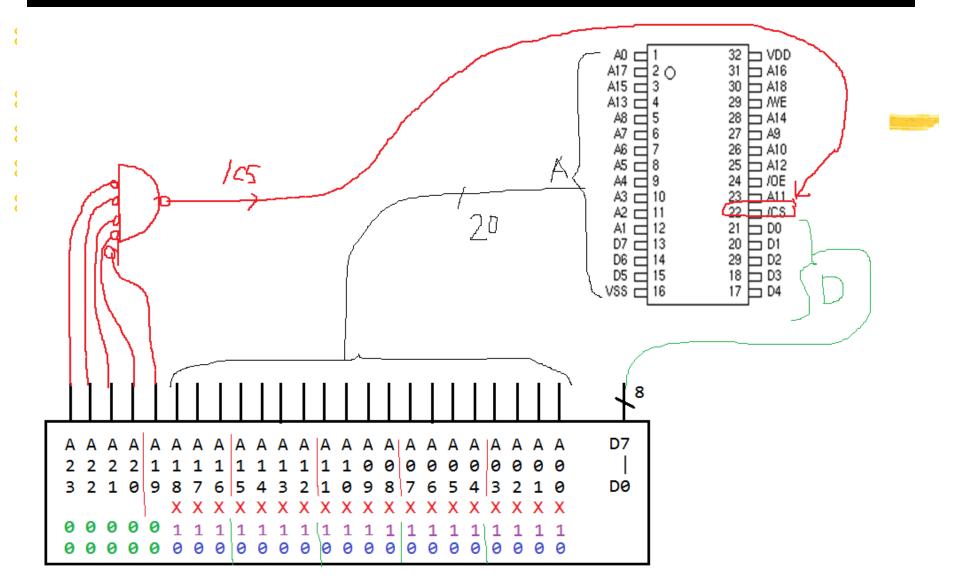

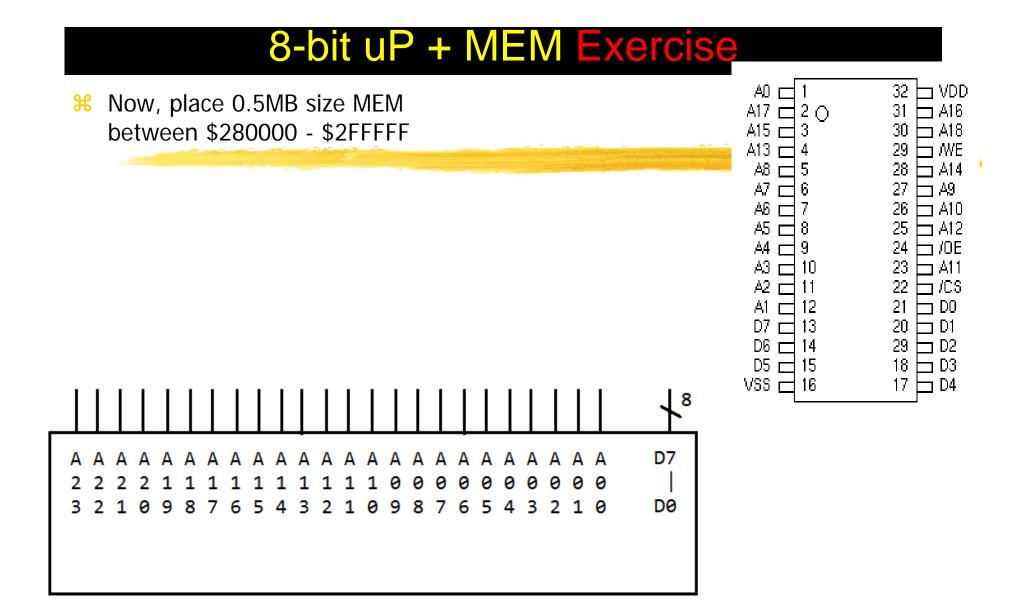

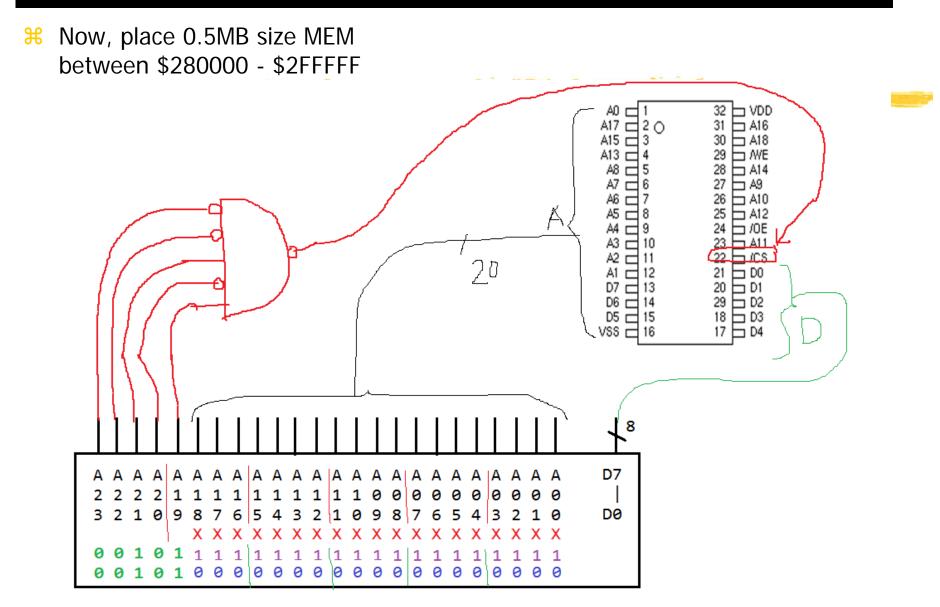

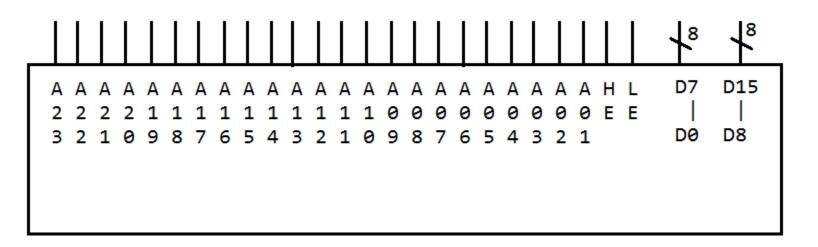

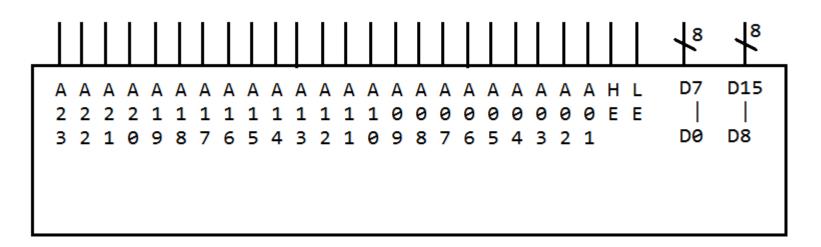

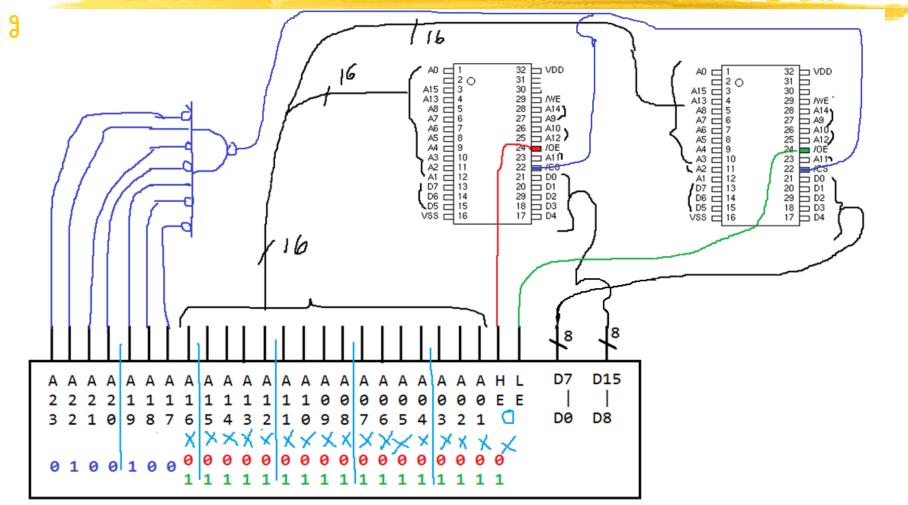

#### 8-bit uP + MEM Exercise

| H           | uP has 2 <sup>24</sup> =24MB=16MB memory space:<br>000000 - FFFFFF<br>MEM has 2 <sup>19</sup> =0.5MB | A0 1<br>A17 20<br>A15 3<br>A13 4                                                                     | 32 DVDD<br>31 A16<br>30 A18<br>29 WE                                                                             |

|-------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| ж<br>ж<br>ж |                                                                                                      | A8 5<br>A7 6<br>A6 7<br>A5 8<br>A4 9<br>A3 10<br>A2 11<br>A1 12<br>D7 13<br>D6 14<br>D5 15<br>VSS 16 | 28 A14<br>27 A9<br>26 A10<br>25 A12<br>24 //OE<br>23 A11<br>22 //CS<br>21 D0<br>20 D1<br>29 D2<br>18 D3<br>17 D4 |

|             | A A A A A A A A A A A A A A A A A A A                                                                | ▶                                                                                                    |                                                                                                                  |

#### 8-bit uP + MEM Exercise

### 8-bit uP + MEM Exercise

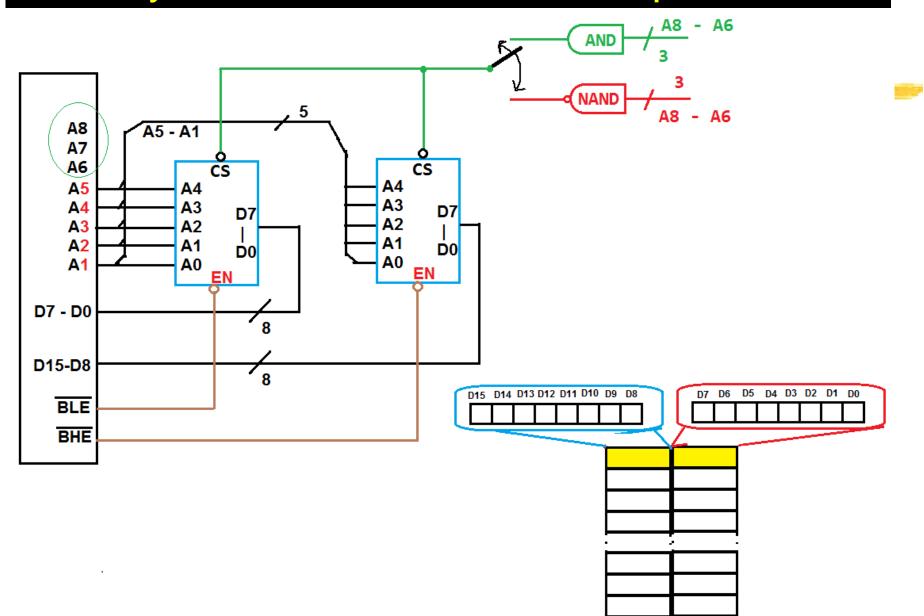

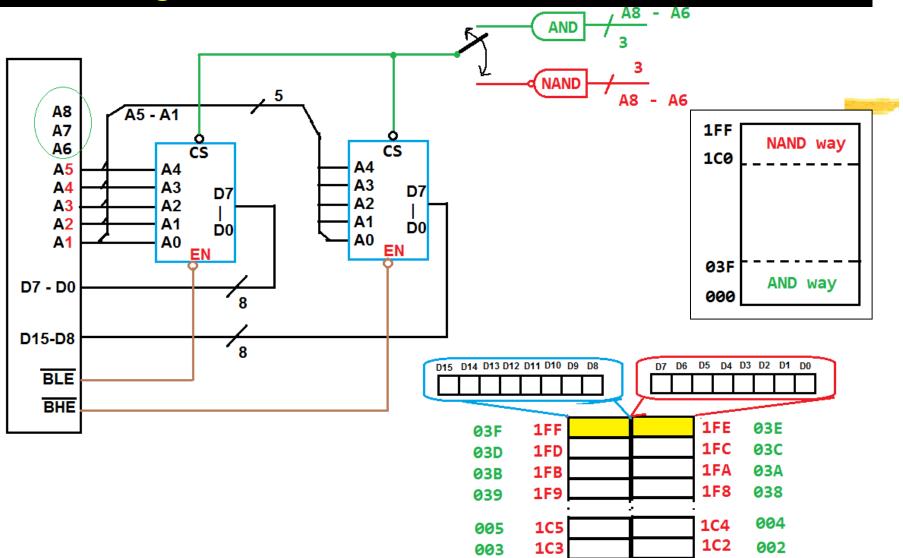

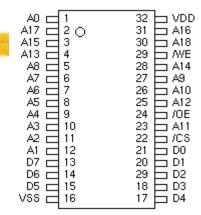

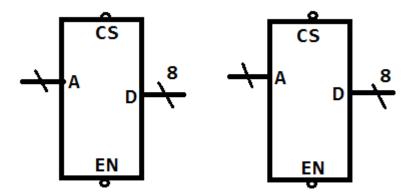

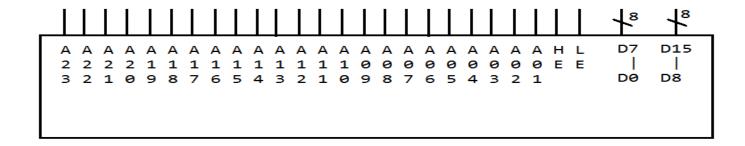

### 16-bit uP + MEM

- # uP does not have A0

- BHE (UDS) and BLE (LDS), instead.

- µP Addr ← → MEM Addr

- △ A19 A1 (uP): A18 A0 (MEM)

- △ Left-Over Addr (uP): A23- A20

- BHE and BLE controls which MEM (or ADDRESS LOCATION) to access

- BHE LOW: Upper MEM (upper or odd address location)

- BLE LOW: Lower MEM (lower or even address location)

- Both BHE amd BLE low: both address locations

| A0<br>A17 | 1<br>2 O | 32<br>31 |             |                              |

|-----------|----------|----------|-------------|------------------------------|

| A15       | 3        | 30       |             | and the second second second |

| A13  A8   | 4        | 29<br>28 |             |                              |

| A7 🗆      | 6        | 27       | E A9        |                              |

| A6        | 7        | 26       | EÃ10        |                              |

| A5 🖂      | 8        | 25       | E A12       |                              |

| A4 🗖      | 9        | 24       | ⊟ /0E       |                              |

| A3 🗖      | 10       | 23       | 🗖 A11       |                              |

| A2 🗖      | 11       | 22       | ⊨ /cs       |                              |

| A1 🗆      | 12       | 21       |             |                              |

| D7 🗆      | 13       | 20       | Þ <u>01</u> |                              |

| D6 🗆      | 14       | 29       |             |                              |

|           | 15       | 18       |             |                              |

| VSS 🗖     | 16       | 17       | ⊨ D4        |                              |

### 16-bit uP + MEM

- uP does not have A0 H

- BHE (UDS) and BLE (LDS),  $\overline{}$

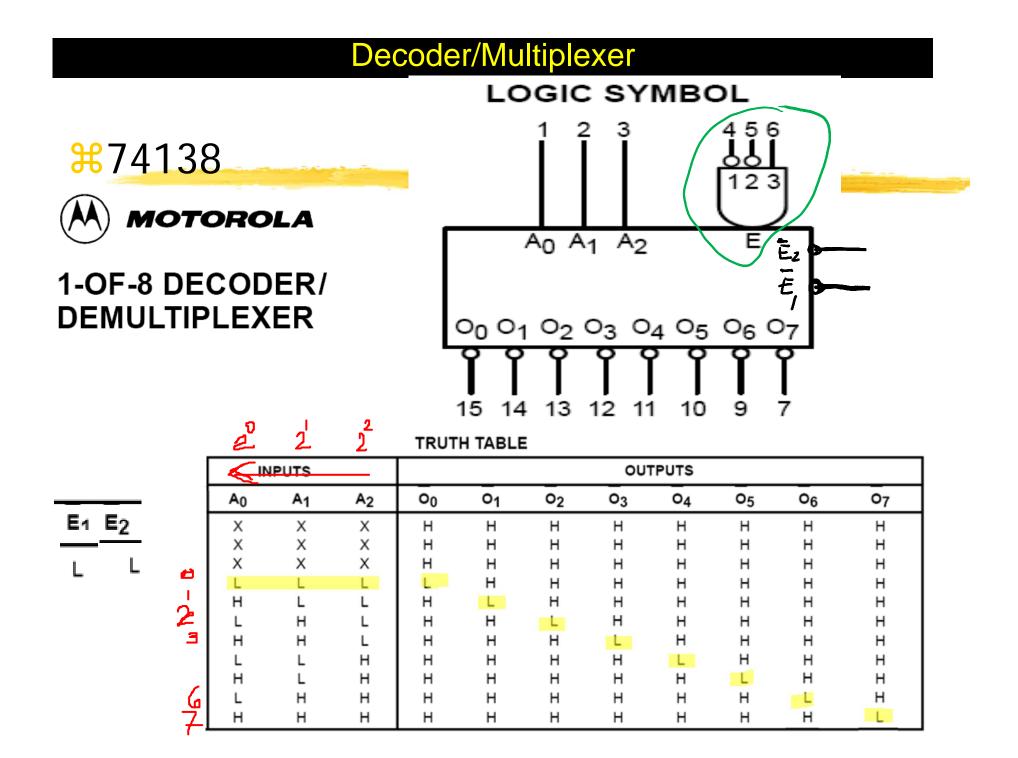

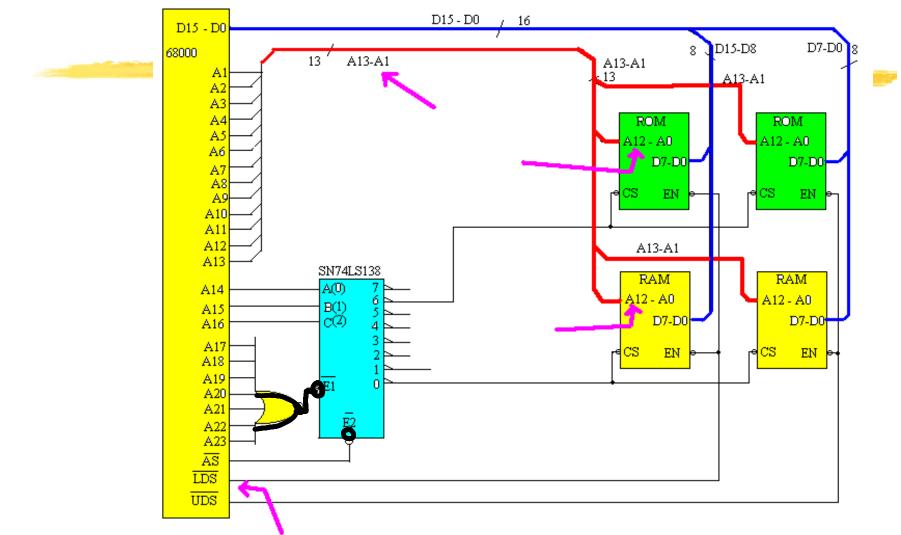

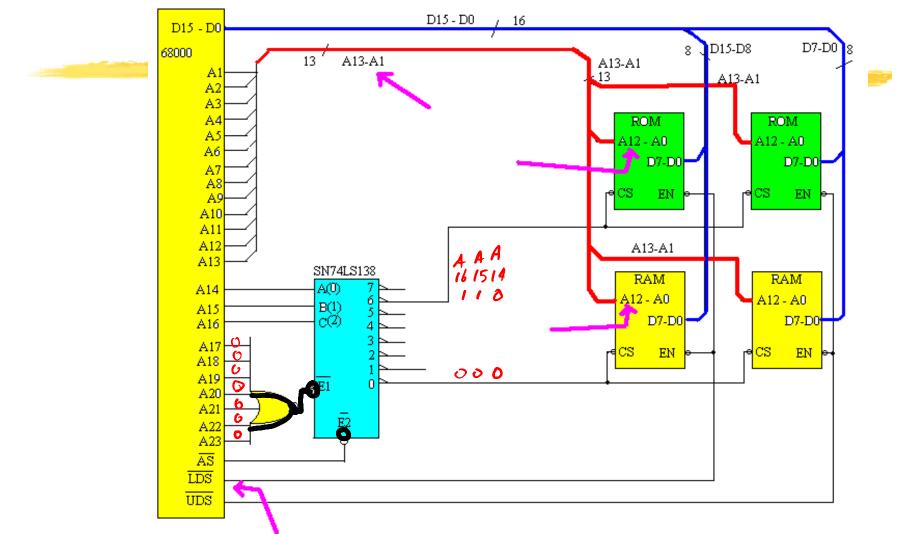

### **Memory Decoding**

₩ Q: 64K Word (or 128 KB) of RAM, with it's starting address at \$480000

**※** A: 64KB → 16 lines each MEM

△ Range: \$480000 - \$49FFFF

△ BHE and BLE for A<sub>0</sub> line → Enable

△ Upper address lines → CS for both MEM

#### Memory Decoding ----- Name\_

₩ Q: 64K Word (or 128 KB) of RAM

$\Re$  A: 64KB  $\rightarrow$  16 lines each MEM

Range: \$480000 - \$49FFFF

### **Memory Decoding**

₩ Q: 64K Word (or 128 KB) of RAM, with it's starting address at \$480000

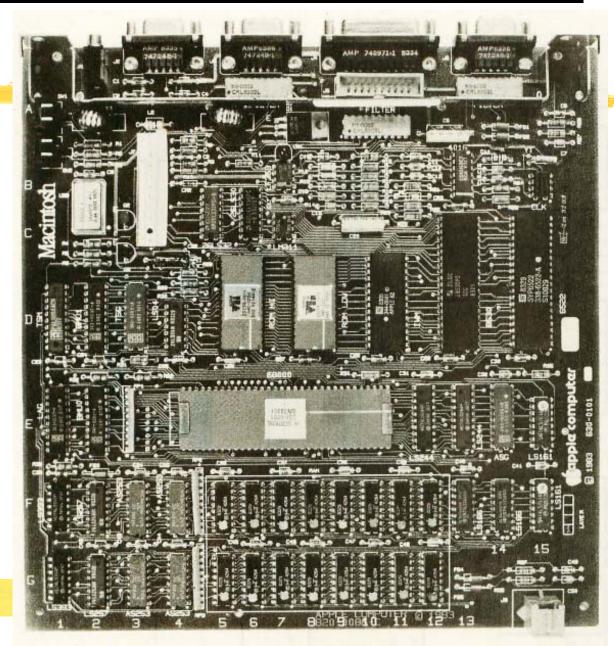

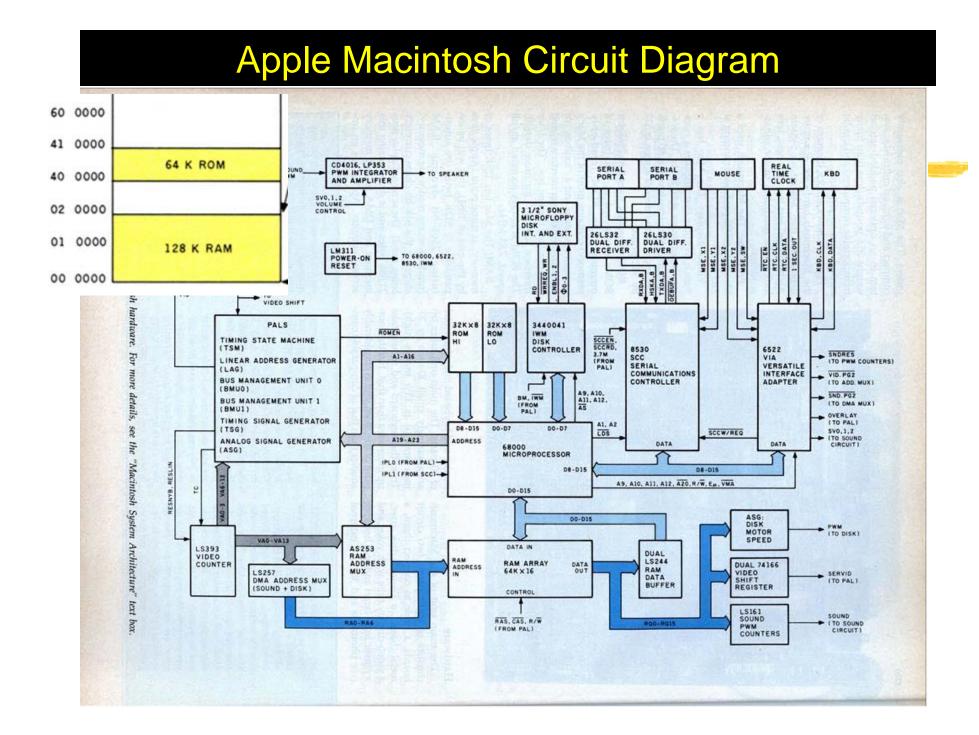

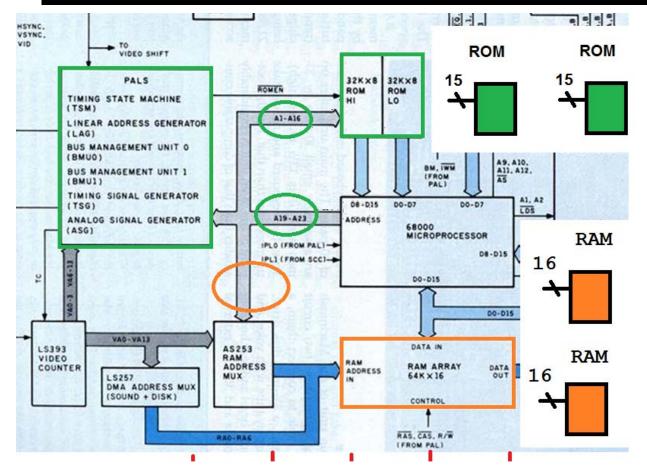

### Apple Macintosh Classic

- CPU: 8MHz Motorola 68000

- Hintroduced in 1984

- Hemory: 128KB (512KB in later version) RAM, 64KB ROM

- 3.5" 400KB Floppy Disk

- Herein Content and MacPaint Representation Application: MacWrite and MacPaint

At a Glance

Name

Macintosh

Manufacturer

(408) 996-1010

Dimensions

Weight

lbs.

model

Apple Computer

20525 Mariani Ave.

Cupertino, CA 95014

9.75 by 9.75 by 13.5 inches

**Power Requirements**

Main unit, keyboard and mouse-22.7

105-130 V AC, 60 Hz (U.S. model); 85-135 V AC, 50/60 Hz (international

- ₭ Mouse

- ₩ 9" B&W Monitor

- ₭ Keyboard

- ₭ Serial Port (DB-9)

- Printer Port

- ₭ Addressing: 24-bit

#### Memory

#### 128K bytes of RAM, 64K bytes of ROM Standard Configuration Main unit with 128K bytes of RAM, 64K

bytes of ROM, integral Sony 3½-inch disk drive, 9-inch video monitor, two serial ports; external mechanical mouse; external keyboard

#### Mass Storage

One Sony 3<sup>1</sup>/<sub>2</sub>-inch disk drive; 3<sup>1</sup>/<sub>2</sub>-inch disk holds 400K bytes and is encased in a rigid plastic housing

#### Video Display

9-inch monitor, noninterlaced 60.15-Hz image, 512- by 342-pixel resolution

#### Pointing Device Mechanical mouse

Keyboard

#### Detached keyboard; 58 keys (59 in international version); autorepeat; two-key rollover

#### Hardware Options

Second disk drive, keypad, Imagewriter printer, security kit (for chaining computer to table)

#### Software Options

Mac Paint (drawing program), Mac Write (a simple word processor), Mac BASIC, Mac Pascal, others (see text)

#### Prices

Standard system, \$1995-\$2495; Mac Paint and Mac Write (together), bundled at no charge for the first 100 days, \$195 (for the two) thereafter; Macintosh Pascal, BASIC, Logo, Terminal, and Assembler/Debugger, \$99 each; Mac Draw and Mac Project, \$125 each; keypad, \$99; second disk drive, \$395; Imagewriter printer, \$495

### Apple Macintosh Classic

- ₭ CPU: 8MHz Motorola 68000

- Hemory: 128KB (512KB in later version) RAM, 64KB ROM

The product-design goals of small size, light weight, and moderate end-user cost encouraged us to create a low-power, low component-count design.

Macintosh System Architecture by Burrell C. Smith

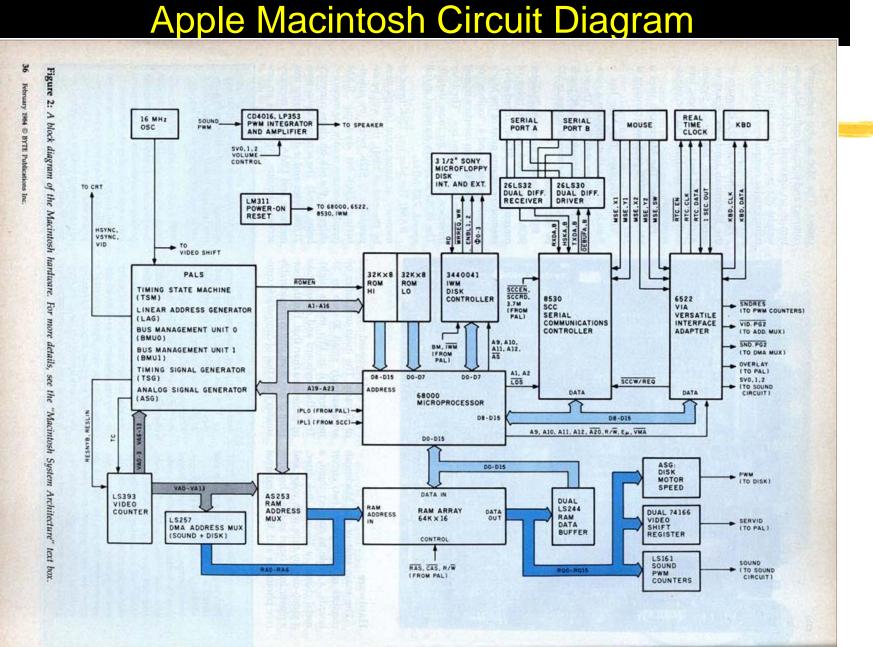

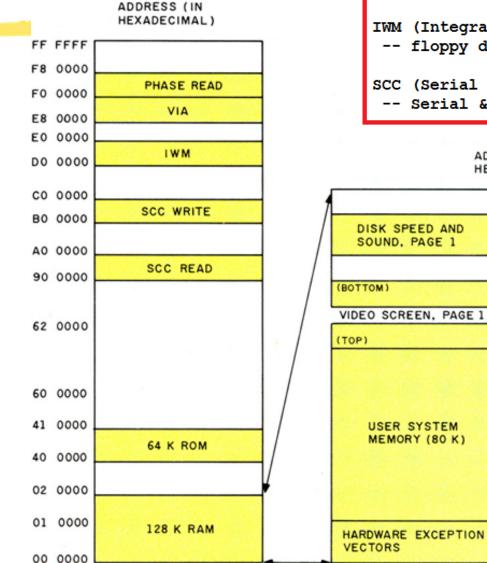

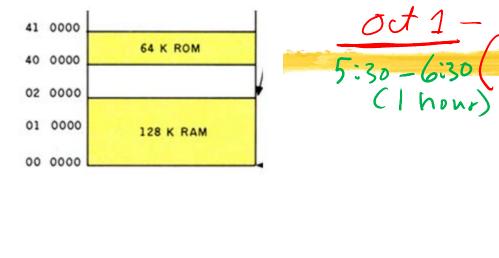

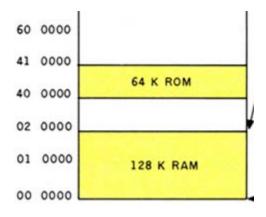

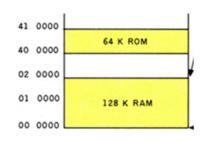

## Memory Map (for Apple Macintosh)

VIA(Versatile Interface Adapter) ---general I/O

IWM (Integrated Woz Machine)

-- floppy disk

ADDRESS (M

HEXADECIM

01 FFFF

01 FFE

01 F00

01 FC/

01 A700

00 0100

00 000

SCC (Serial Communications Controller)

-- Serial & Mouse

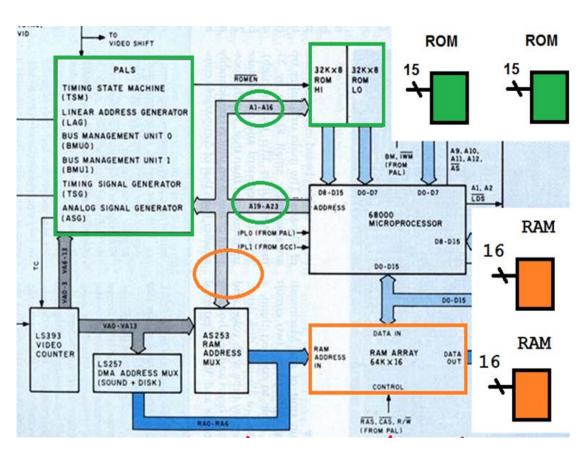

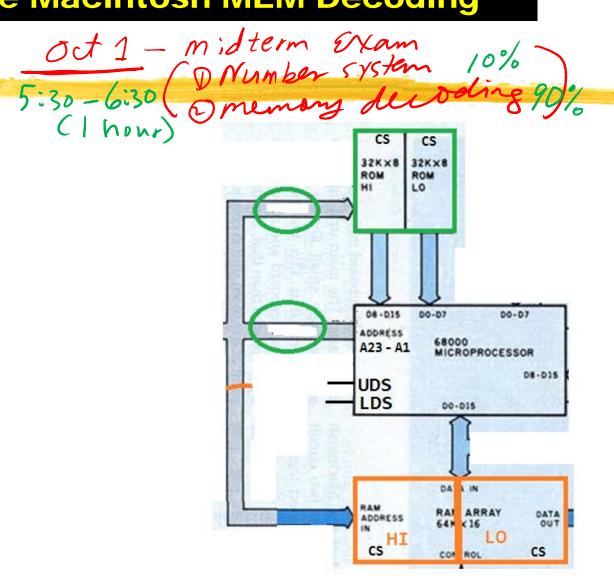

## **Apple Macintosh MEM Decoding**

Burrell was working in Apple's service department when he helped Bill Atkinson add more memory to an Apple II computer in an innovative fashion. Bill recommended him to Jef Raskin, who was looking for a hardware engineer to help him with his newly formed Macintosh project.<sup>[1]</sup> As a member of the design team,<sup>[2]</sup> Burrell designed five different motherboards during the course of Macintosh development, all of which used techniques based on Programmable Array Logic (PAL) chips to achieve maximum functionality with a minimal chip count.

#### **Design for Apple Macintosh MEM Decoding**

## **Apple Macintosh MEM Decoding**

### **Design for Apple Macintosh MEM Decoding**

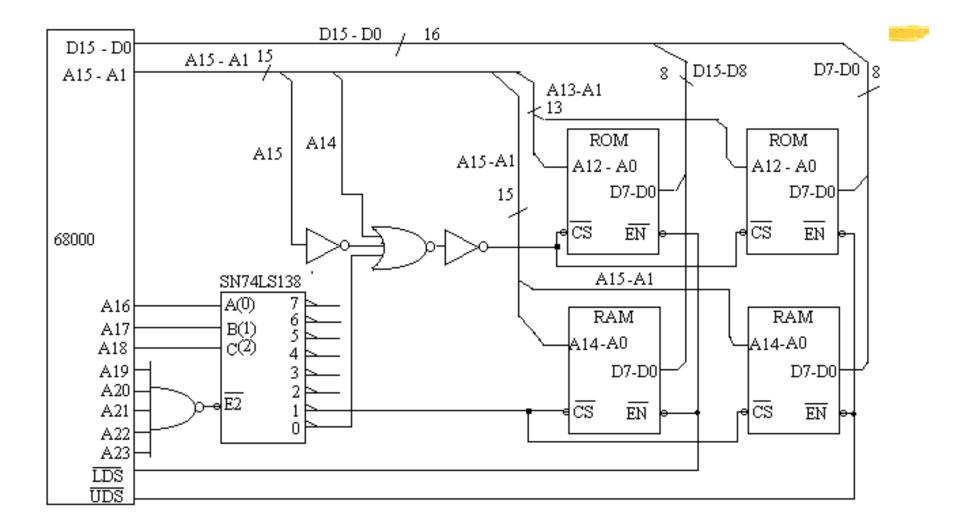

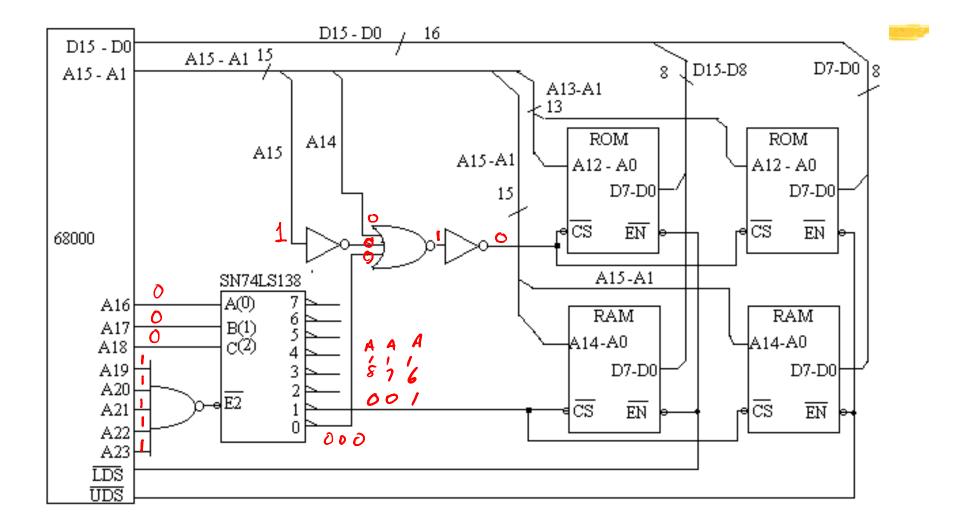

### Memory Decoding with Byte/Word Access

- **H** Questions:

- △ 1. Size of ROM

- 2. Size of RAM

- 🔼 3. Memory Map

### Memory Decoding with Byte/Word Access - SOLUTION

- **H** Questions:

- △ 1. Size of ROM

- 2. Size of RAM

- 3. Memory Map

# Solution 2

Rom (Left):

$$2^{13} = 2^3 \cdot K = 8 \times B$$

(Upper Byte)

Rom (Right):  $8 \times B$  (Lower Byte)

RAM (Left):  $8 \times B$  (Upper Byte)

RAM (Right):  $8 \times B$  (Upper Byte)

$\overline{E} = A23 \sim A17 = 0$  [MEM SEL]

$0 \leftarrow A16 \sim A14 = 0$  [RAM]

$0 \leftarrow A16 \sim A14 = 0$  [RAM]

\$ 000 000 00 3 FFF \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 018000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 008000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 0000 \$ 00000 \$ 0000000 \$ 00000 \$ 0000000 \$ 0000000 \$ 00000 \$ 000000 \$ 0000000 \$ 000

### Can You Draw a Memory Map of this?

### Can You Draw a Memory Map of this? - SOLUTION

## Solution 3

RAM

$$\{2^{15} = 32 \times B^{3}\} \times 2 \rightarrow 64 \times B$$

ROM  $\{2^{13} = B \times B^{3} \times 2 \rightarrow 16 \times B$

$\langle \text{MEM SELECTION} \rangle$

$\bigcirc \overline{E_{2}} : A^{23} \sim A^{19} = 1$  ( $\overline{E_{N}}$ )

$\bigcirc \overline{C_{3}} \text{ for } RAM$  (1):  $A^{18}=0, A^{17}=0, A^{16}=1$

$\bigcirc \overline{C_{3}} \text{ for } ROM [complex]: A^{18}=0, A^{17}=0, A^{16}=0$

$A^{14}=0$

$A^{15}=1$

RAM

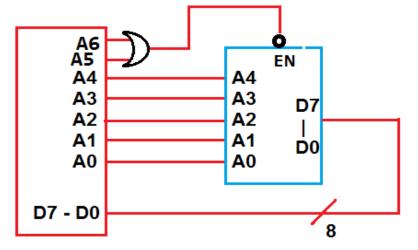

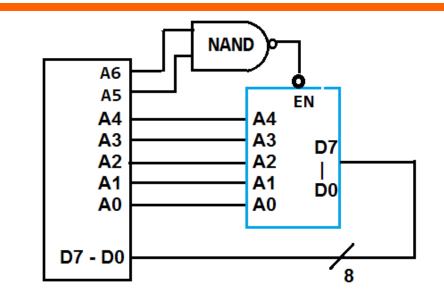

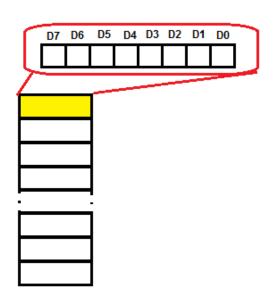

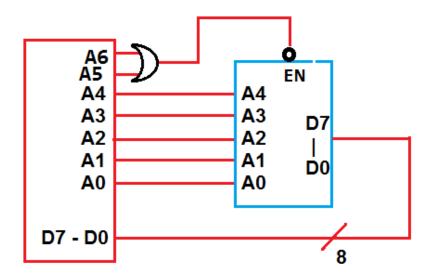

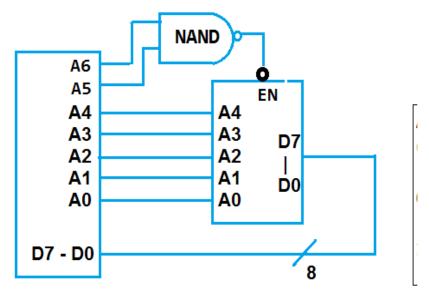

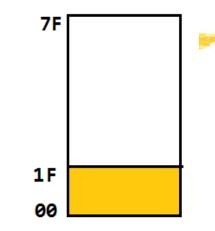

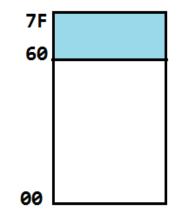

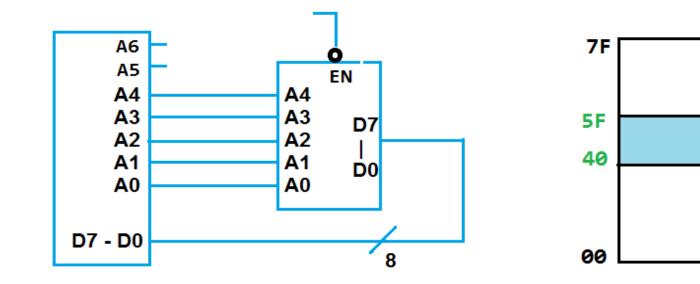

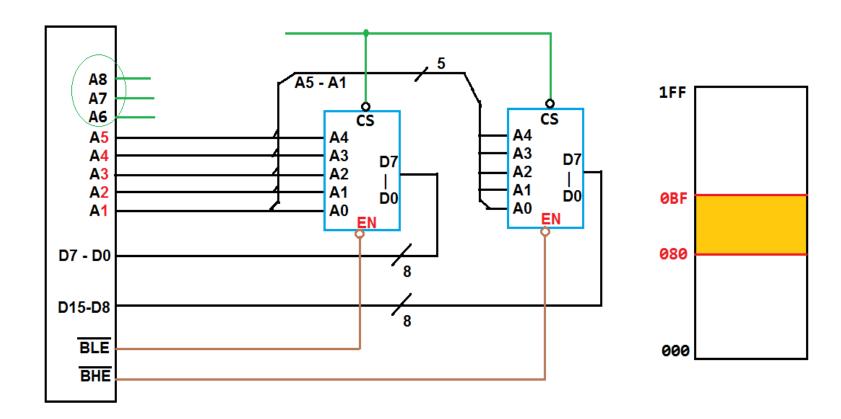

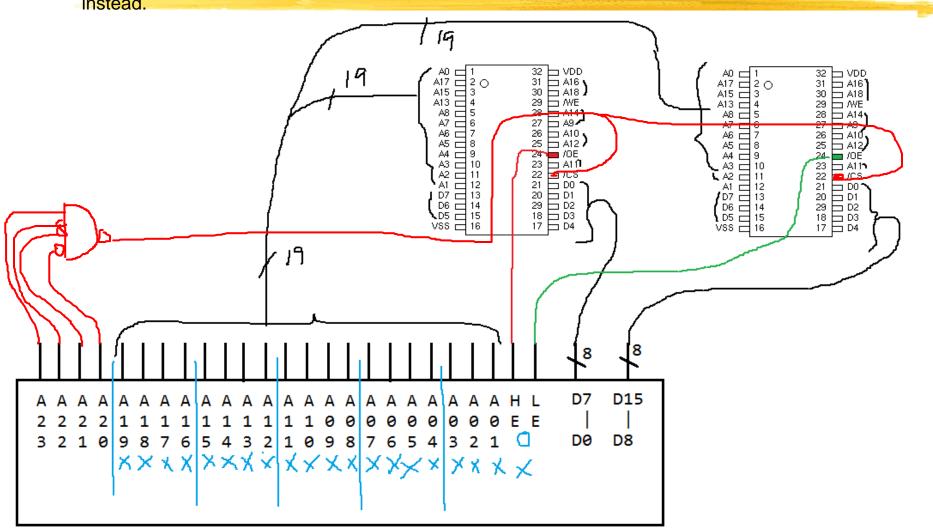

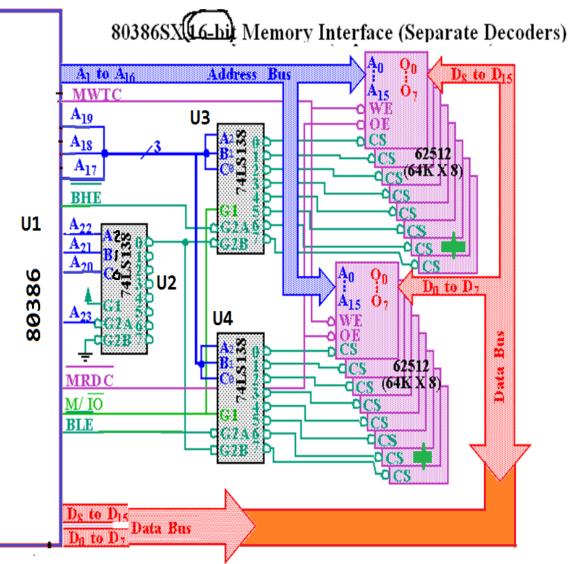

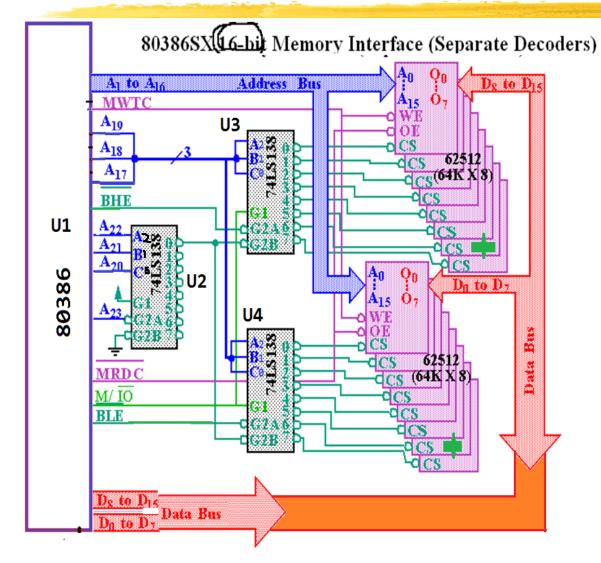

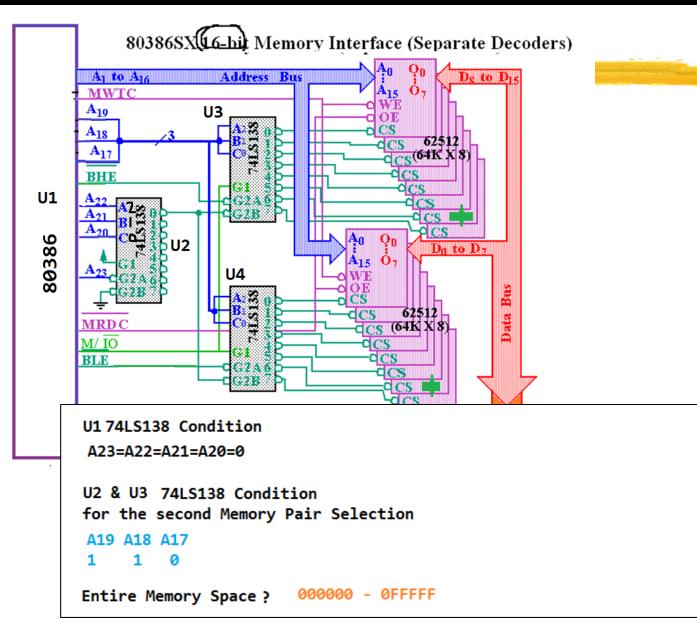

## Intel 80386 Memory – Decoding – Quiz

- A pair of memory pack (High and Low bytes) Eight (8) 64KB Memory Chips

- At each pack, each memory chip is SELECTED (/CS) by an output from U3 (High Byte) and U4 (Low Byte), which are enabled by the single output from U2.

- **Question**: Find the address range of the second chip of the pair of memory pack. (Green Mark)

- Ignore MWTC and MRDC, M/IO lines (they are for Write, Read, Memory or I/O operations, respectively)

## Intel 80386 Memory – Decoding – Quiz

- Find the address range of the second chips of the memory pair. (Green Mark)

- **K** Quiz: Individual Work (Name:\_

### Intel 80386 Memory – Decoding – Class Activity

90