### EECE416 Microcomputer Fundamentals & Design

### **Computer Architecture**

Dr. Charles Kim Howard University

### "Computer Architecture"

#### **#** Computer Architecture

- Art of selecting and interconnecting hardware components to create functional unit (or computer)

- $\triangle$  2 points of view

#### **⊠Instruction Set architecture (ISA)**:

- the code that a CPU reads and acts upon. It is the machine language (or assembly language), including the instruction set, word size, memory address modes, processor registers, and address and data formats

- Interface between H/W and S/W

- programmers' point of view

#### **Microarchitecture** (or computer organization):

- describes the data paths, data processing elements and data storage elements, size of cache, and describes how they should implement the ISA

- Optimization

- Power Management

- system designers' point of view.

#### Analogy:

⊠ House (rooms) – views of builders and residents

⊠Car – views of manufacturers (or mechanics) and drivers

## **Micro-Architecture**

#### **K** Computer System

CPU (with PC, Register, SR) + Memory

#### **Hicro-Architecture:**

- "conceptual design and fundamental operational structure of a computer system"

- "blueprint and functional description of requirements and design implementations of a computer"

- focusing on the way the CPU performs and accesses memory.

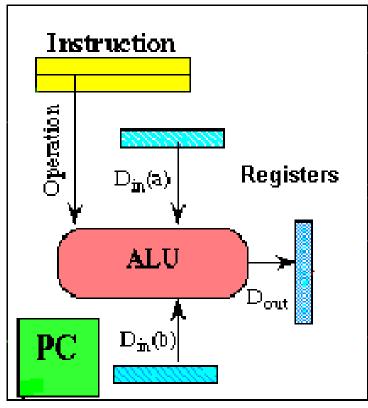

#### Microprocessor

## **Micro-Architecture**

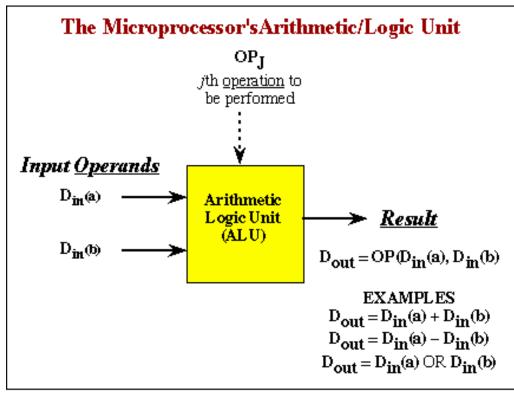

#### ALU (Arithmetic Logic Unit)

- Fundamental building block of CPU

- Binary Full Adder

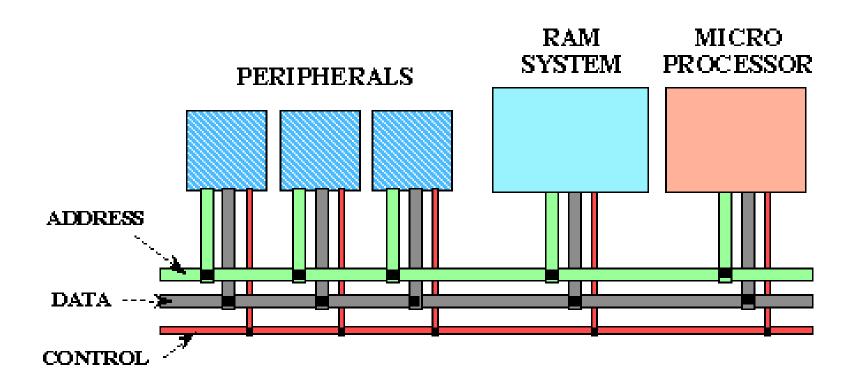

## **Microprocessor Bus**

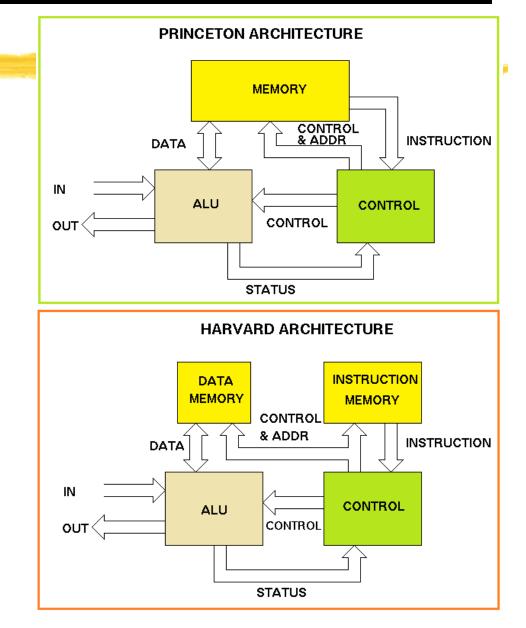

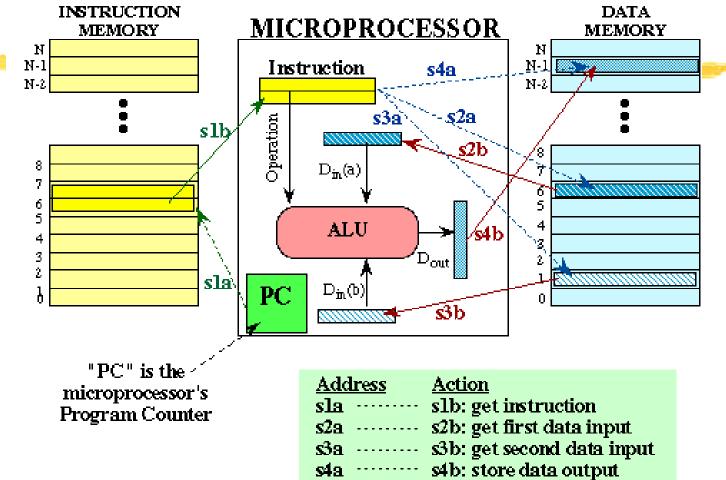

## Architecture by CPU+MEM organization

- Princeton (or von Neumann) Architecture

MEM contains both Instruction and Data

- ✓Von Neumann Bottleneck CPU <→ Memory</p>

- Cache

- Harvard Architecture

- Data MEM and Instruction MEM

- Higher Performance via Pipeline

- Better for DSP

- Higher MEM Bandwidth

# "Pipeline"?

## **#Instruction Pipeline**

An **instruction pipeline** is a technique used in the design of **computers** to increase their instruction throughput (the number of instructions that can be executed in a unit of time). Pipelining does not reduce the time to complete an instruction, but increases instruction throughput by performing multiple operations in parallel.

The term pipeline is an analogy to the fact that there is fluid in each link of a pipeline, as each part of the processor is occupied with work.

| Instr. No.     |   | Pipeline Stage |    |     |     |     |     |

|----------------|---|----------------|----|-----|-----|-----|-----|

| 1              | F | ID             | ΕX | мем | WB  |     |     |

| 2              |   | IF             | ID | ΕX  | мем | WB  |     |

| 3              |   |                | IF | ID  | ΕX  | мем | WB  |

| 4              |   |                |    | IF  | D   | ΕX  | МЕМ |

| 5              |   |                |    |     | IF  | ID  | EX  |

| Clock<br>Cycle | 1 | 2              | 3  | 4   | 5   | 6   | 7   |

Basic five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back). In the fourth clock cycle (the green column), the earliest instruction is in MEM stage, and the latest instruction has not yet entered the pipeline.

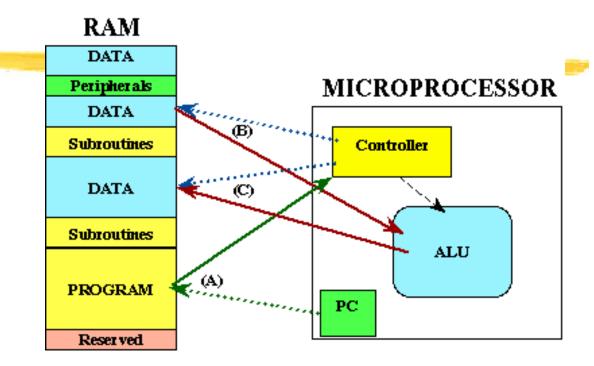

### **Princeton Architecture**

1.Step (A): The

address for the instruction to be next executed is read into

2. **Step (B):** The controller "decodes" the instruction

3.**Step (C)**: Following completion of the instruction, the controller provides the address, to the memory unit, at which the data result generated by the operation will be stored.

•CPU can be either reading an instruction or reading/writing data from/to the memory.

•Both cannot occur at the same time since the instructions and data use the same bus system

#### Harvard Architecture

- 1. CPU can both read an instruction and perform a data memory access at the same time.

- 2. Faster for a given circuit complexity because instruction fetches and data access do not contend for a single memory pathway.

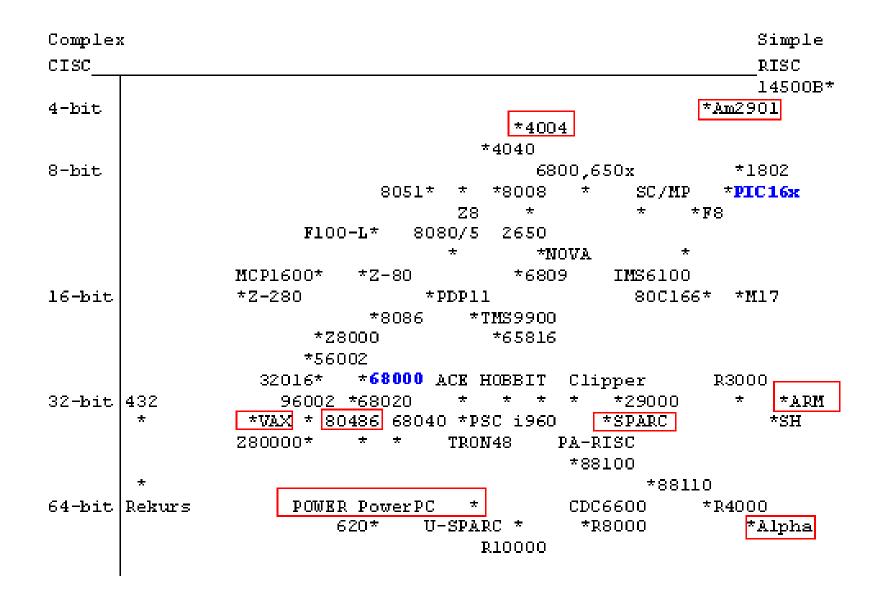

### Architecture by Instructions and Executions

- #CISC (Complex Instruction Set Computer)

- Variety of instructions for complex tasks directly to hardware

- Easy to translate high-level language to assembly

- ○Complex Hardware

- Instructions of varying length

- #RISC (Reduced Instruction Set Computer)

- ⊡ Fewer and simpler instructions

- Each instruction takes the same amount of time

- △Less complex hardware

- ☐ High performance microprocessors

- Pipelined instruction execution (several instructions are executed in parallel)

## CISC

#Architecture of prior to mid-1980's

IBM390, Motorola 680x0, Intel80x86

#Basic Fetch-Execute sequence to support a large number of complex instructions

#Complex decoding procedures

#Complex control unit

#One instruction achieves a complex task

# RISC

**#**Favorable changes for RISC

- Caches to speed instruction fetches

- □ Dramatic memory size increases/cost decreases

- ⊡Better *pipelining*

- Advanced optimizing compilers

- Characteristics of RISC

- Instructions are of a uniform length

- Increased number of registers to hold frequently used variables (16 - 64 Registers)

- Central to High Performance Computing

#### **Processor Classification**

-

### Intel inside?

## **Kext PCs or Mobile Computing**

Devices

Smart phones

∴ Apple Processors

∴ ARMs

∴ Qualcomm

△ Mobile Devices – Smartphones, MP3, Digicam (on ARM)

△ Run on Intel's x86? --- Intel's wish

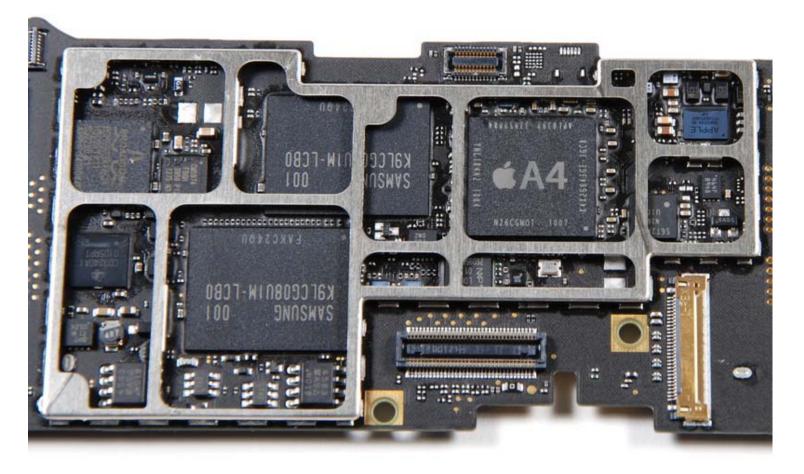

## What's inside?

### HiPhone: 1GHz-A4 microprocessor, 256MB Samsung RAM,

# What's inside?

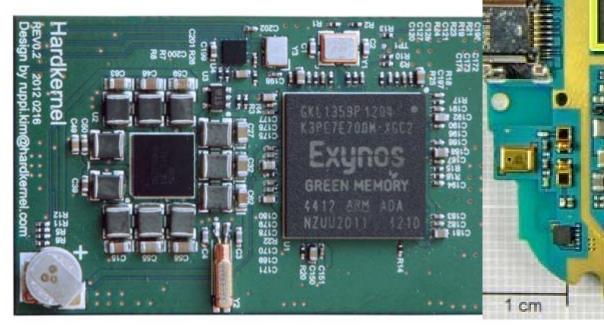

#### Samsung Galaxy

- Samsung Exynos quad-core A9 processor

- ☐ 1GB Memory

- ☐ Intel Wireless processor

- Broadcom Global Navigation Satellite System receiver

# What's Inside?

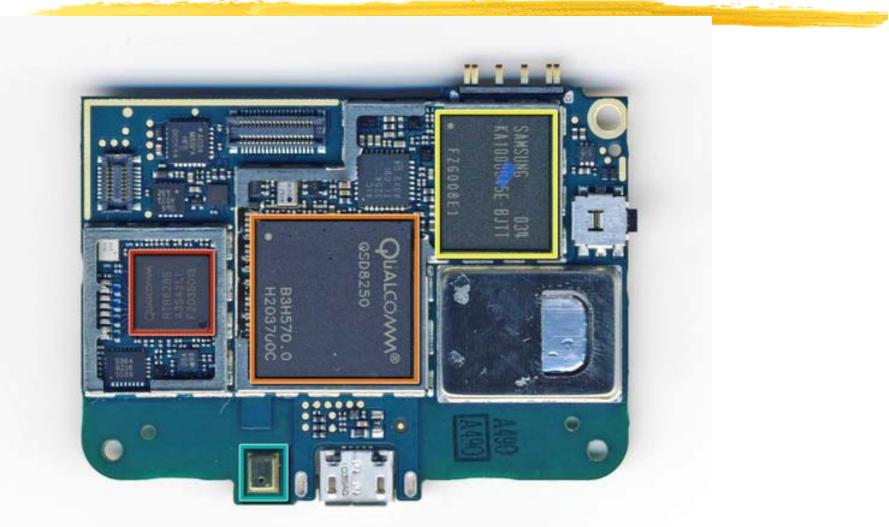

### **HTC**

# What's inside?

#### **XNokia Lumina**

### △1.4GHz Qualcomm CPU, 512MB RAM, 16GB Storage,

💭 วัสธุ่มใสอุปปปร.

### INTEL VS. ARM ("Advanced RISC Machine")

ARMs

- No chip hardware license only (powerful and variety of licensees) → cell phones etc

- SoC device (CPU + I/O + Peripherals + Memory + etc)

# INTEL

- Does not want to License x86 (Lesson from AMD)

- △ New approach for SoC: Atom based X86 SoC

- **Recent Stride with "Intel Atom Inside"**

- Main processor for Laptops and Netbooks and Tablets

- Motorola Phones: Razr

Intel Atom

| (inte<br>Ator | n <sup>°</sup> inside <sup>°</sup> |

|---------------|------------------------------------|

| duced         | 2008–present                       |

| nmon          | Intel                              |

| nufacturer(s) |                                    |

| . CPU clock   | 800 MHz to 2 GHz                   |

Proc

| Troduced                   | 2000 present                             |

|----------------------------|------------------------------------------|

| Common<br>monufo sturo (a) | Intel                                    |

| manufacturer(s)            |                                          |

| Max. CPU clock             | 800 MHz to 2 GHz                         |

| FSB speeds                 | 400 MHz to 667 MHz                       |

| Min. feature size          | 45nm                                     |

| Instruction set            | x86, x86-64 (not for the N and Z series) |

| Cores                      | 1,2                                      |

| Package(s)                 | 441-ball µFCBGA                          |

| Core name(s)               | Silverthorne<br>Diamondville             |

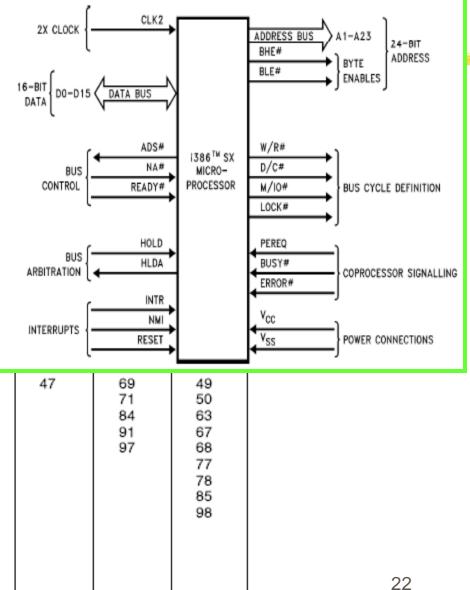

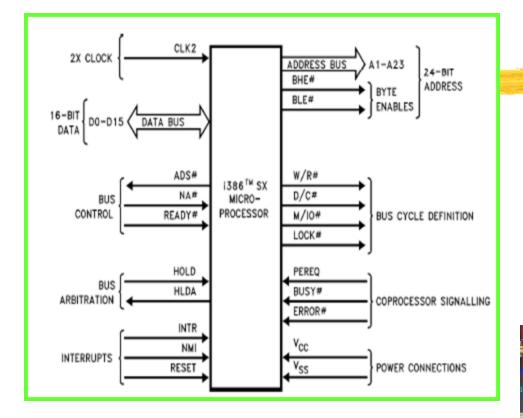

## Intel 386 - Brief

3668

$\cap$

HLĎ

HOLD

READY

000000

A20

A18

A17

$V_{\rm CI}$

A14

V<sub>SS</sub> A12 A11 A10 A9 A8

/cc

A6

> A4

D A3

5

53

53

5:

- # Address: A23- A1 (where is A0?)

BI E# and BHE# ("Byte Enable")

- BLE# and BHE# ("Byte Enable")

- 🔀 Data: D15 D0

- Control

|                                                      |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |                                                                                | 12<br>13<br>14<br>15<br>16                                                                             | TOP VIEW |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|

| Address                                              | Data                                                                                                                                                                                                                                                    | Control                                                                                                                                                                                                                                                                                                                                                                                                                       | N/C                                                      | v <sub>cc</sub>                                                                | V <sub>SS</sub>                                                                                        |          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccc} D_0 & 1 \\ D_1 & 100 \\ D_2 & 99 \\ D_3 & 96 \\ D_4 & 95 \\ D_5 & 94 \\ D_6 & 93 \\ D_7 & 92 \\ D_8 & 90 \\ D_9 & 89 \\ D_{10} & 88 \\ D_{11} & 87 \\ D_{12} & 86 \\ D_{13} & 83 \\ D_{14} & 82 \\ D_{15} & 81 \\ \end{array}$ | ADS#       16         BHE#       19         BLE#       17         BUSY#       34         CLK2       15         D/C#       24         ERROR#       36         FLT#       28         HLDA       3         HOLD       4         INTR       40         LOCK#       26         M/IO#       23         NA#       6         NMI       38         PEREQ       37         READY #       7         RESET       33         W/R#       25 | 20<br>27<br>29<br>30<br>31<br>43<br>44<br>45<br>46<br>47 | 8<br>9<br>10<br>21<br>32<br>39<br>42<br>48<br>57<br>69<br>71<br>84<br>91<br>97 | 2<br>5<br>11<br>12<br>13<br>14<br>22<br>35<br>41<br>49<br>50<br>63<br>67<br>68<br>77<br>78<br>85<br>98 |          |

### **Review on Number Systems**

|     | Binary      | Hexadecimal | Decimal |  |

|-----|-------------|-------------|---------|--|

| 1.  | 100         |             |         |  |

| 2.  | 10101101    |             |         |  |

| 3.  | 1101110101  |             |         |  |

| 4.  | 11111011110 |             |         |  |

| 5.  | 1000000001  |             |         |  |

| 6.  |             | 8EF         |         |  |

| 7.  |             | 10          |         |  |

| 8.  |             | A52E        |         |  |

| 9.  |             | 70C         |         |  |

| 10. |             | 6BD3        |         |  |

| 11. |             |             | 100     |  |

| 12. |             |             | 527     |  |

| 13. |             |             | 4128    |  |

| 14. |             |             | 11947   |  |

| 15. |             |             | 59020   |  |

## Intel 386 - Brief

- Address: A23- A1 (where is A0?)BLE# and BHE# ("Byte Enable")

- 🔀 Data: D15 D0

- Control

|                                                                                                      |                                                                                  |                                                                                                                                                                |                                                    |                                                                                   |                                                   | CONTROL | READY#                               | PROCESSOR                                          |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|---------|--------------------------------------|----------------------------------------------------|

| Addr                                                                                                 | ress                                                                             | Da                                                                                                                                                             | ata                                                | Contro                                                                            | ł                                                 | ,       |                                      |                                                    |

| A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9                                                   | 18<br>51<br>53<br>54<br>55<br>56<br>58<br>59                                     | D <sub>0</sub><br>D <sub>1</sub><br>D <sub>2</sub><br>D <sub>3</sub><br>D <sub>4</sub><br>D <sub>5</sub><br>D <sub>6</sub><br>D <sub>7</sub><br>D <sub>8</sub> | 1<br>100<br>99<br>96<br>95<br>94<br>93<br>92<br>90 | ADS#<br>BHE#<br>BUSY#<br>CLK2<br>D/C#<br>ERROR#<br>FLT#<br>HLDA                   | 16<br>19<br>17<br>34<br>15<br>24<br>36<br>28<br>3 | BUS     | HOLD<br>HLDA<br>INTR<br>NMI<br>RESET |                                                    |

| A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>A16<br>A17<br>A18<br>A19<br>A20<br>A21<br>A22<br>A23 | 60<br>61<br>62<br>64<br>65<br>66<br>70<br>72<br>73<br>74<br>75<br>76<br>79<br>80 | D <sub>9</sub><br>D <sub>10</sub><br>D <sub>11</sub><br>D <sub>12</sub><br>D <sub>13</sub><br>D <sub>14</sub><br>D <sub>15</sub>                               | 89<br>88<br>87<br>86<br>83<br>82<br>81             | HOLD<br>INTR<br>LOCK#<br>M/IO#<br>NA#<br>NMI<br>PEREQ<br>READY #<br>RESET<br>W/R# | 4<br>40<br>26<br>38<br>37<br>7<br>33<br>25        | 47      | 69<br>71<br>84<br>91<br>97           | 49<br>50<br>63<br>67<br>68<br>77<br>78<br>85<br>98 |

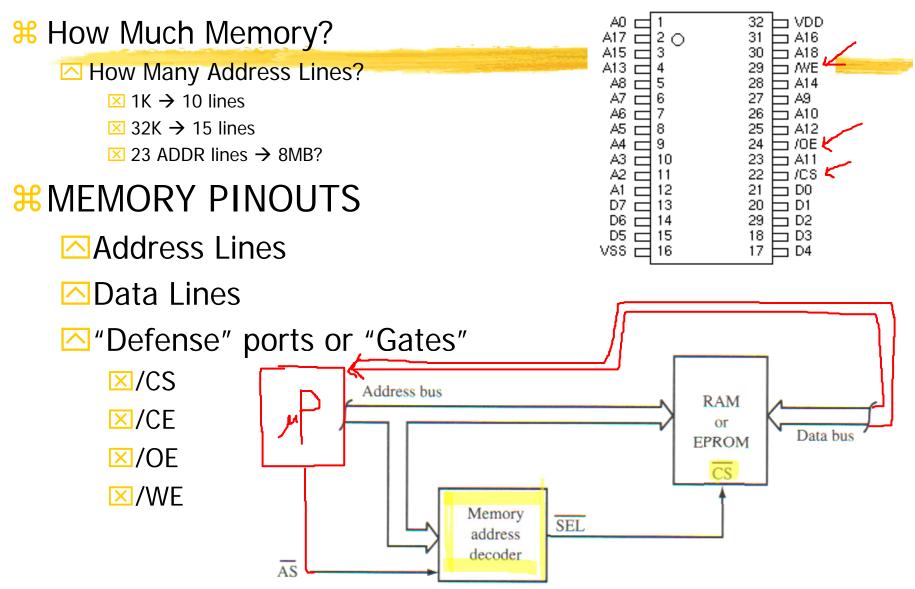

### **Memory Size and Address**

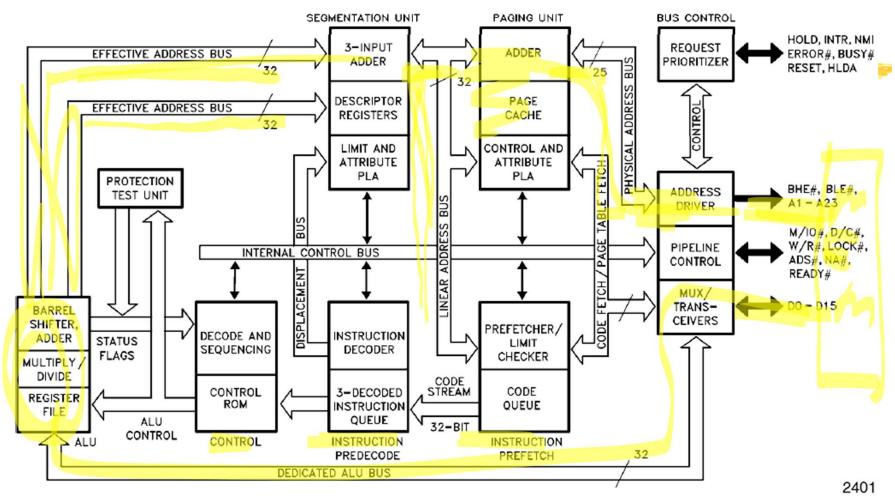

### 386 Micro-Architecture

Intel386<sup>™</sup> SX Pipelined 32-Bit Microarchitecture

#### Connecting with Memory, I/O, and Peripherals

0000

- **%** Single Board Computers

- Processor Boards

- **₭** Kits

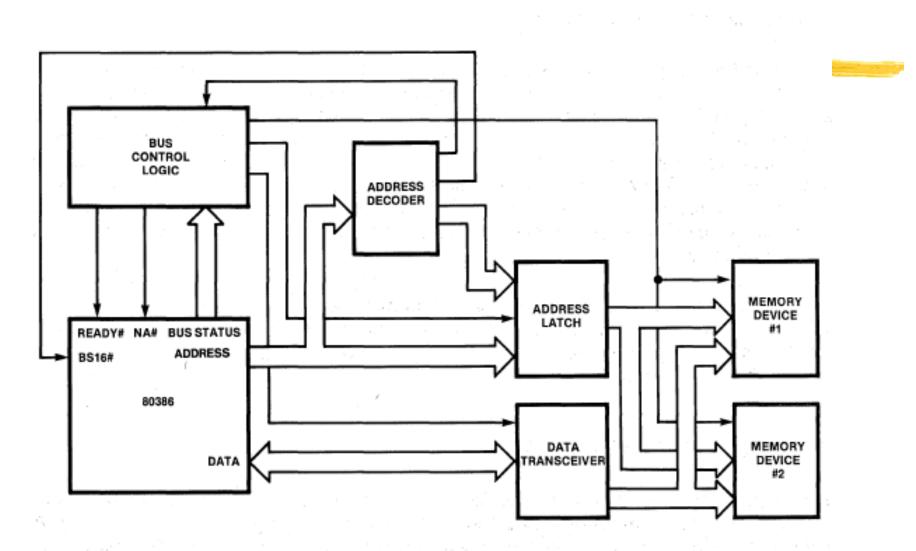

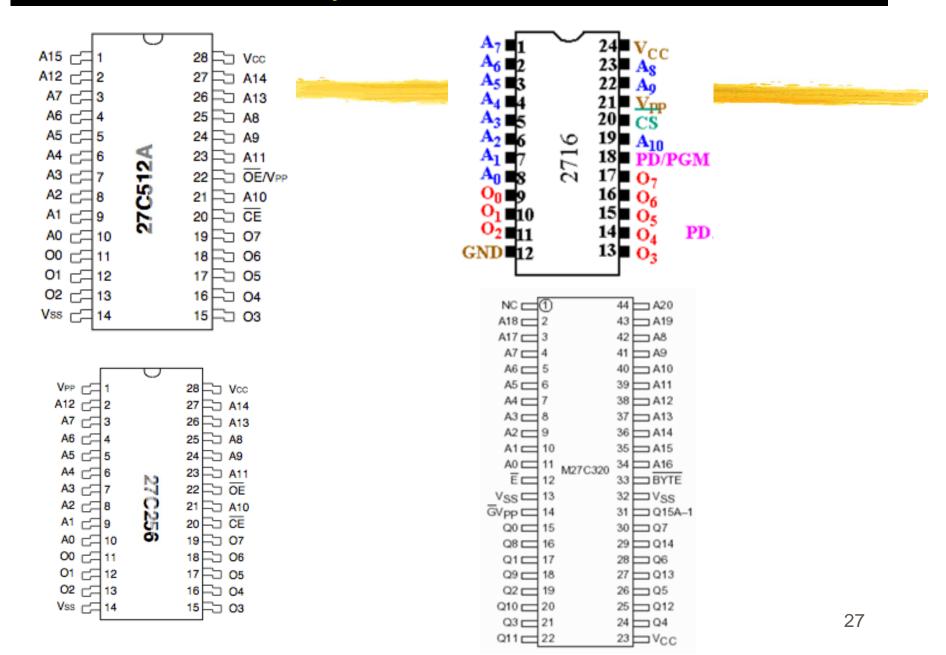

# **Memory Interface**

26

### Memory Size and Address 2

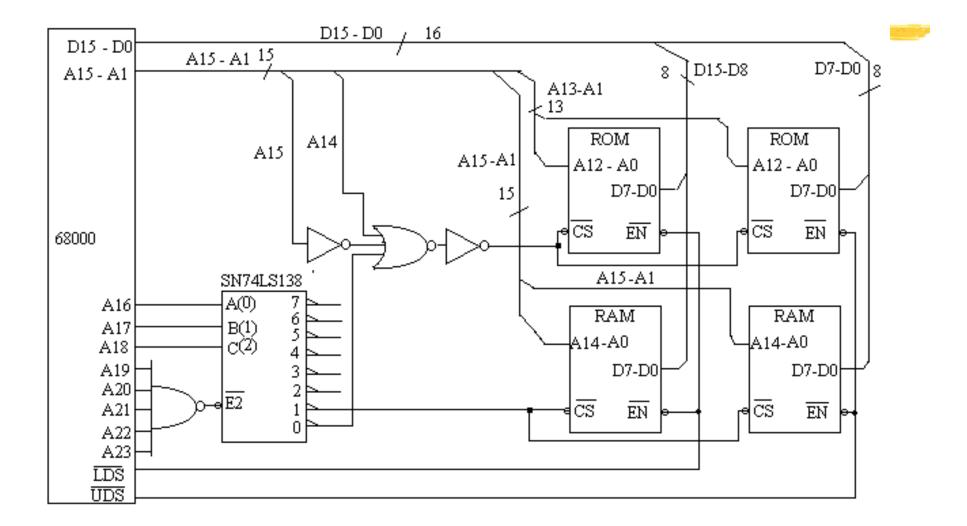

### **Memory Interface**

- Interface between a processor and a (pair) of memory (of smaller than the maximum memory space)

- ₩ Where do we place the memory in the memory space? → "MEMORY DECODING"

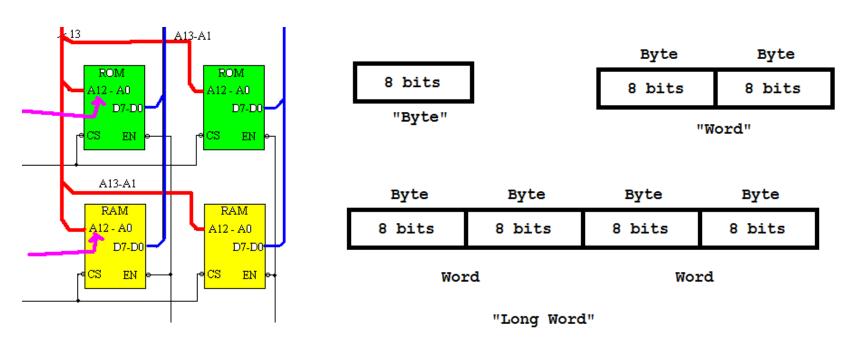

- How to access two MEMs at the same time (for 16bit Data bus)?

- MEM --- Byte Access (8 bits)

- UDS and LDS --- Motorola

- △BLE and BHE --- Intel

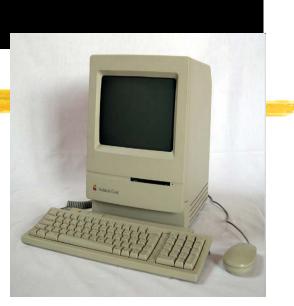

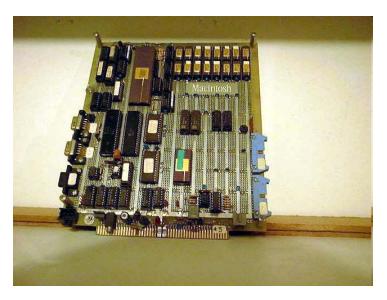

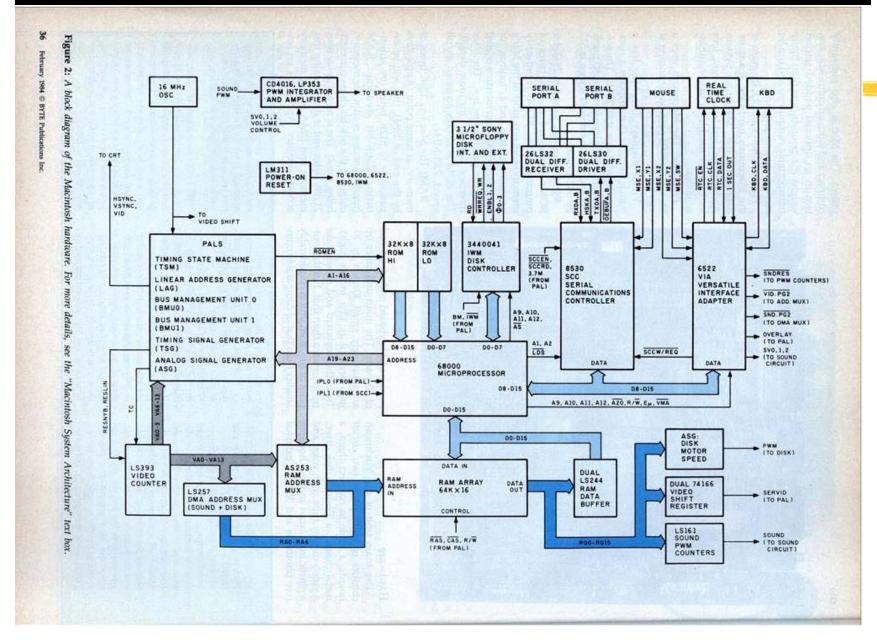

## **Apple Macintosh**

- ₭ CPU: 8MHz Motorola 68000

- Hintroduced in 1984

- Memory: 128KB (512KB in later version) RAM, 64KB ROM

- 8.5" 400KB Floppy Disk

- ₭ Application: MacWrite and MacPaint

- ₿ Mouse

- ¥ 9″ B&W Monitor

- ₭ Keyboard

- ₭ Serial Port (DB-9)

- **#** Printer Port

- ₭ Addressing: 24-bit

### Apple Macintosh Circuit Diagram

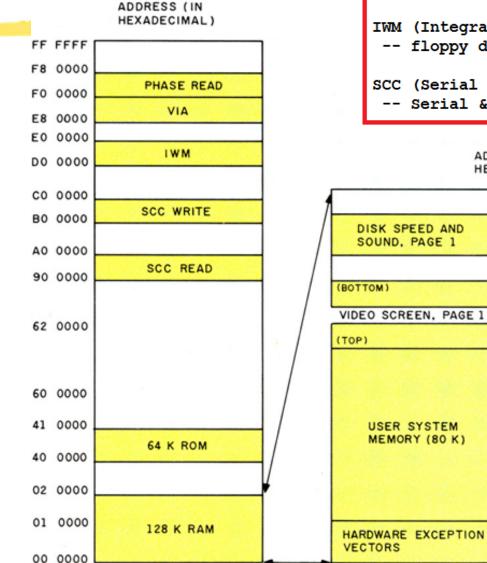

### Memory Map (for Apple Macintosh)

VIA(Versatile Interface Adapter) ---general I/O

IWM (Integrated Woz Machine)

-- floppy disk

ADDRESS (M

HEXADECIM

01 FFFF

01 FFE

01 F00

01 FC/

01 A700

00 0100

00 000

SCC (Serial Communications Controller)

-- Serial & Mouse

31

## Memory Address Decoding

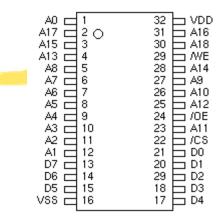

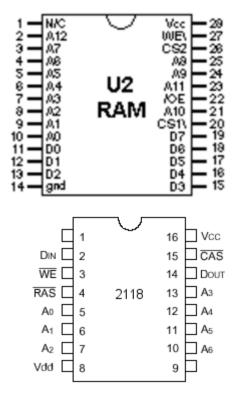

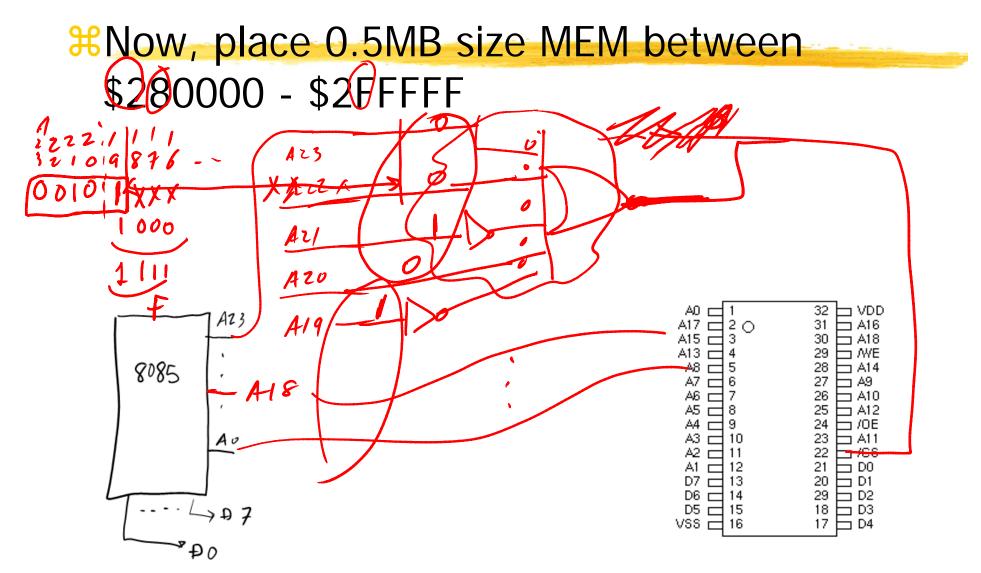

### uP + MEM

32 VDD 31 A16 30 A18 29 WE 28 A14 27 A9 26 A10 25 A12 24 OE 23 A11 22 CS 21 D0 20 D1 29 D2 18 D3 17 D4

| i386 | A23               |

|------|-------------------|

|      |                   |

|      | BHE<br>BLE        |

|      | 7 D15~78<br>77~70 |

| A0 1<br>A17 2 0<br>A15 3<br>A13 4<br>A8 0 5<br>A7 0 6<br>A6 0 7<br>A5 0 7<br>A | 32         VDD           31         A16           30         A18           29         AVE           28         A14           27         A9           26         A10           25         A12           24         /0E           23         A11           22         /CS           21         D0           20         D1           29         D2           18         D3           17         D4 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

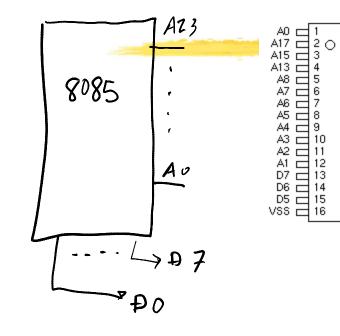

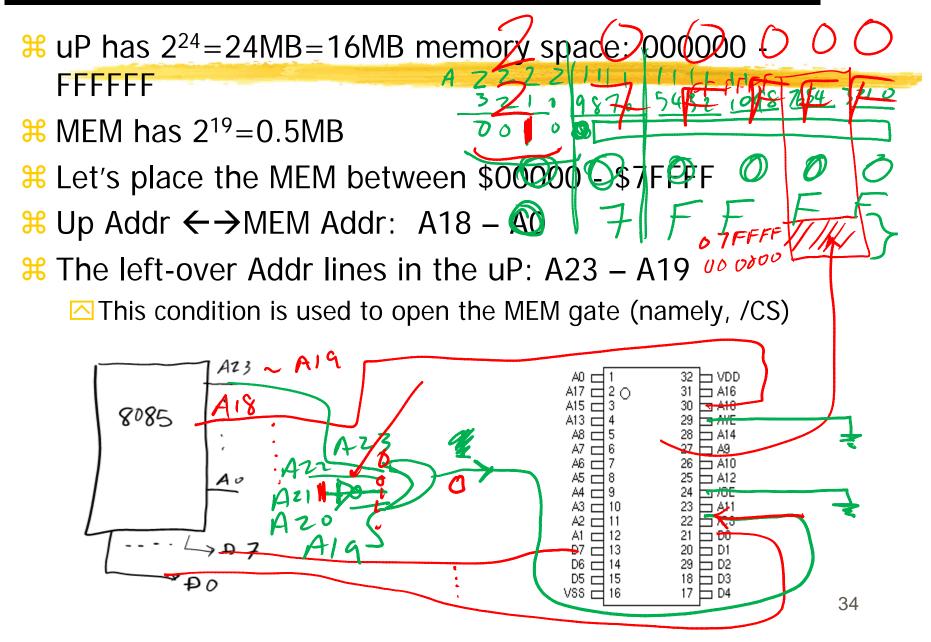

### 8-bit uP + MEM

### 8-bit uP + MEM

35

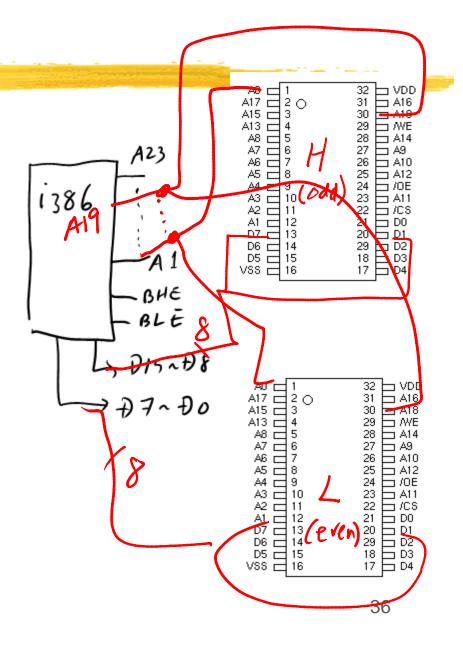

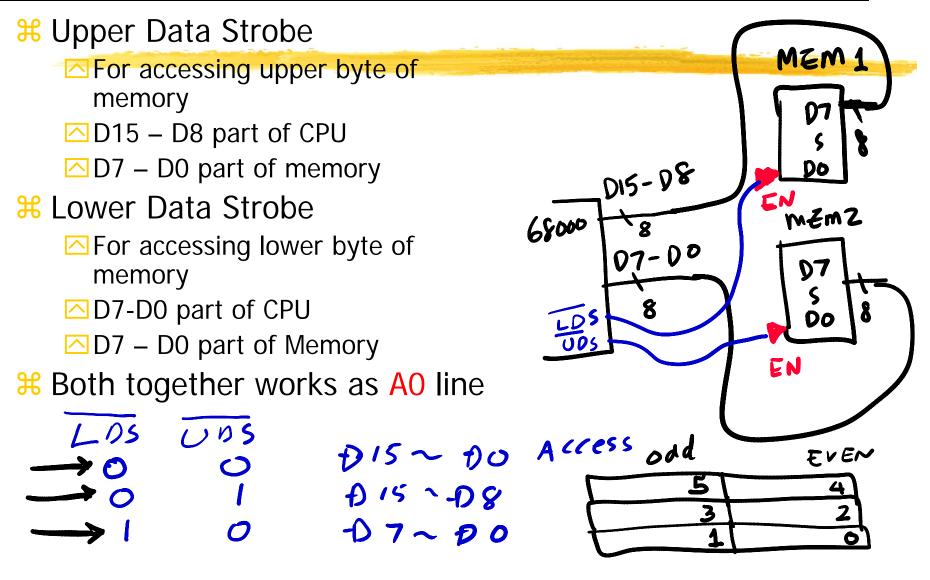

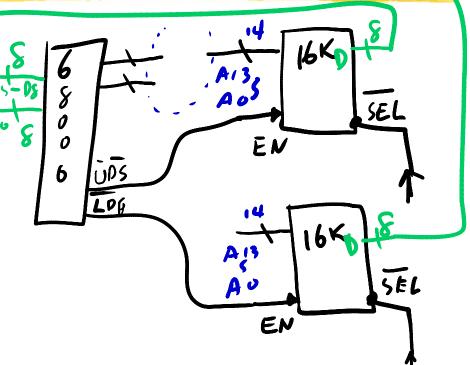

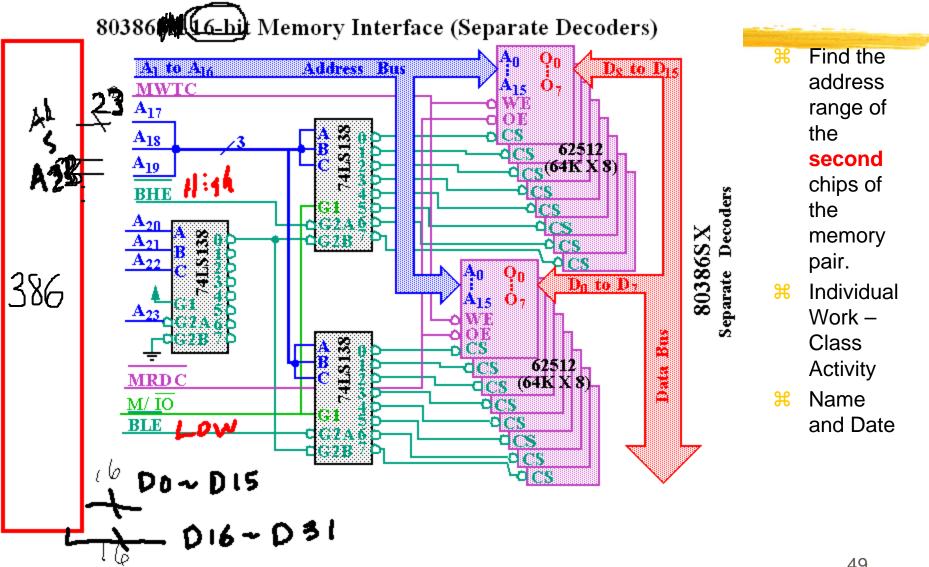

### 16-bit uP + MEM

- ₭ uP does not have A0

- BHE (UDS) and BLE (LDS), instead.

- ₭ uP can access 2 MEMs

- H uP Addr  $\leftarrow \rightarrow$  MEM Addr

- △ A19 A1 (uP): A18 A0 (MEM)

- Left-Over Addr (uP): A23-A20

- BHE and BLE controls which MEM (or ADDRESS LOCATION) to access

- BHE LOW: Upper MEM (upper or odd address location)

- ➢ BLE LOW: Lower MEM (lower or even address location)

- Both BHE amd BLE low: both address locations

# BHE/UDS and BLE/LDS (for 386/68000)

37

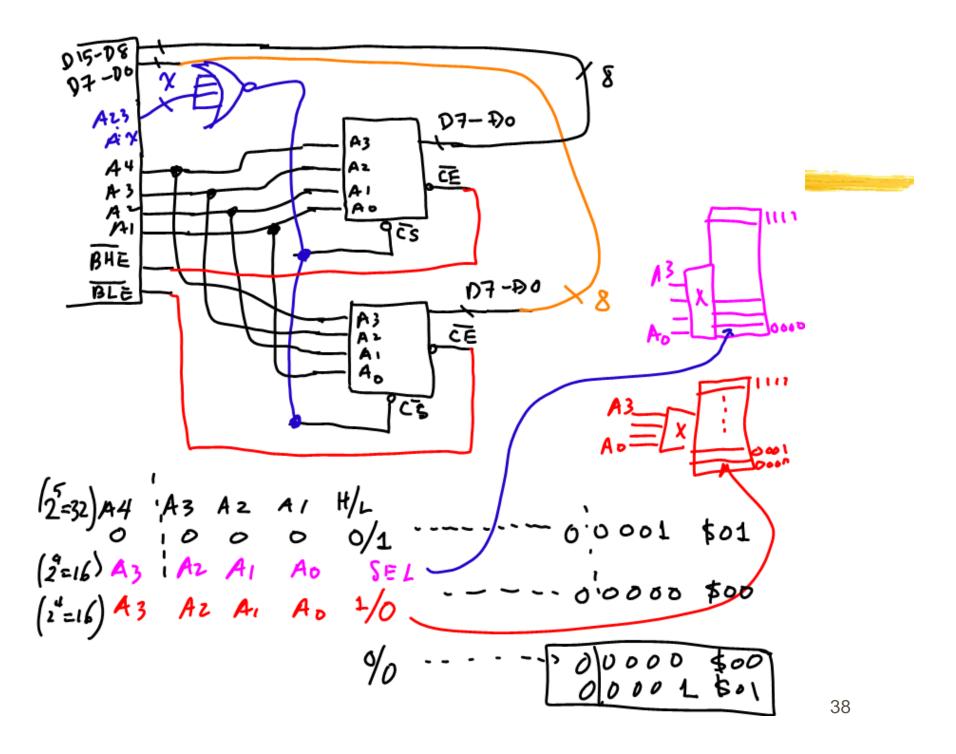

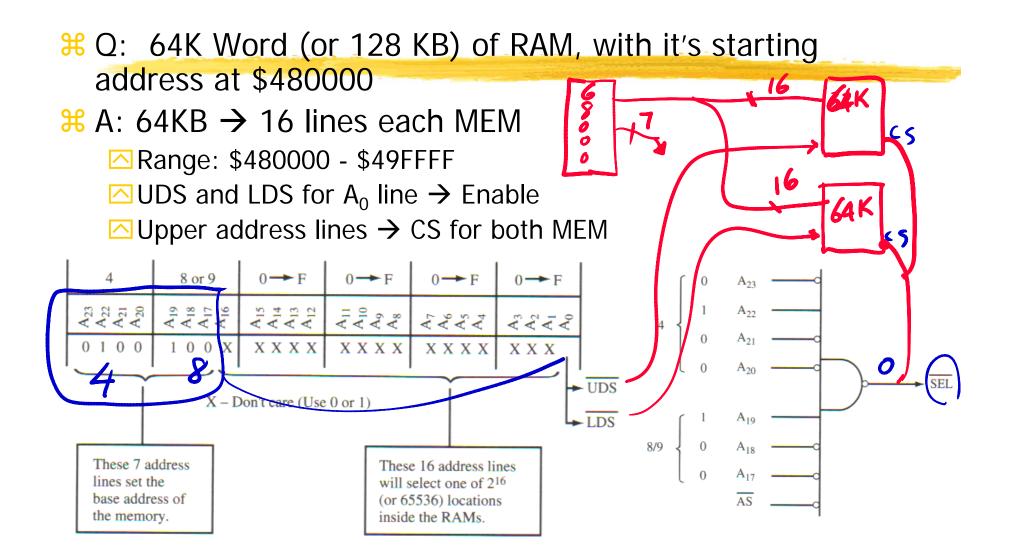

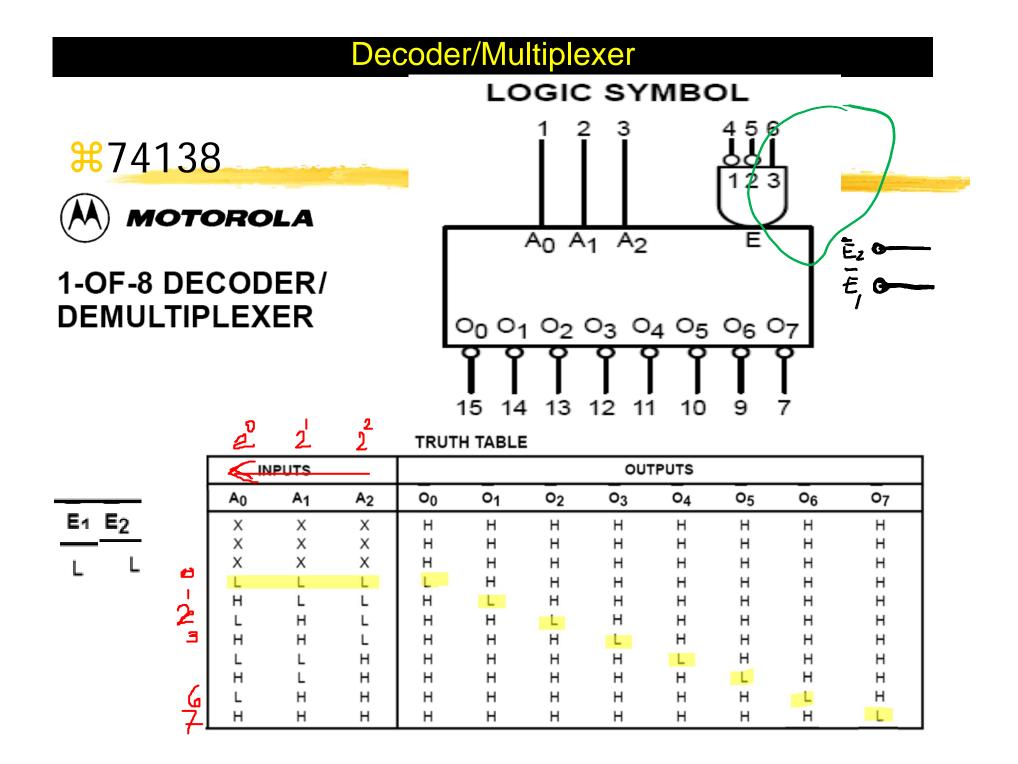

## **Memory Decoding**

# Memory Decoding Example - 1

2.16Byte Roms ₩Q: 16K Word ROM with starting address at \$300000. 8  $\Re$  A: 16KB  $\rightarrow$  14 lines 0 07-00 0 each MEM UPS 6 LOG △\$300000 - \$307FFF OUDS (BHE)/LDS (BLE)  $\rightarrow$  /CE  $\square$  Upper Address  $\rightarrow$  /CS

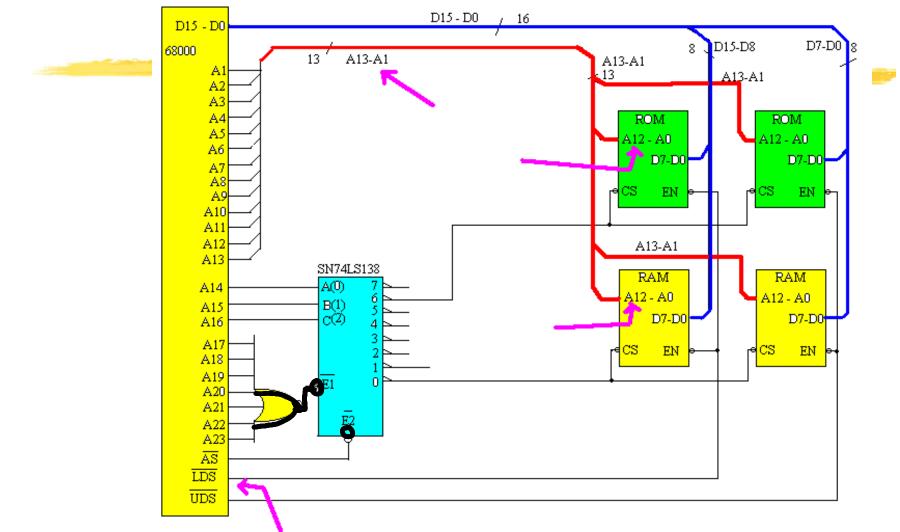

### Memory Decoding with Byte/Word Access – 2 HW

- **H** Questions:

- △ 1. Size of ROM

- 2. Size of RAM

- 3. Memory Map

### Can You Draw a Memory Map of this? - 3

## Intel 80386 Memory – Decoding – Class Activity

49

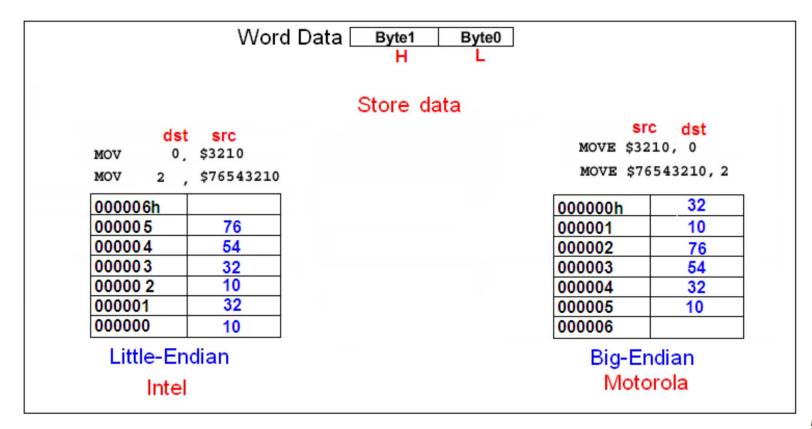

# **Multiple Address Access Issues**

#### 8-bit processor

△ Access one address with a byte data

#### ₭ 16-bit processor

- Can access two address spaces (Even and Odd)at a single execution with 2-byte (or "Word") data

- Where do we store each of the 2 bytes to each of the 2 address spaces?

### **Big-Endian vs. Little-Endian**

- Big-Endian: Words are stored with the lower 8- bits in the higher of the two storage locations: Motorola

- "Big guy ends at lower address"

- Little- Endian: Lower-order byte stored in the lowest address) processors: Intel 80x86 family

- △ Little guys ends at lower address"

# "Endianness"

#### **#** Endian or Endian-Architecture

- how multi-byte data is represented by a computer system and is dictated by the CPU architecture of the system

- Not all computer systems are designed with the same endian architecture

- ☐ Issues with software and interface

Computer System Endianness

#### Common file formats

| Platform              | Endian Architecture | Little Fudien Connet Die Fudien Connet Verieble en Di Fudien Connet |                         |                                       |

|-----------------------|---------------------|---------------------------------------------------------------------|-------------------------|---------------------------------------|

|                       |                     | Little-Endian Format                                                | Big-Endian Format       | Variable or Bi-Endian Format          |

| ARM*                  | Bi-Endian           | BMP (Windows* & OS/2)                                               | PSD (Adobe Photoshop*)  | DXF (AutoCAD*)                        |

| DEC Alpha*            | Little-Endian       | GIF                                                                 | IMG (GEM Raster*)       | PS (Postscript*, 8 bit                |

| HP PA-RISC 8000*      | Bi-Endian           | FLI (Autodesk Animator*)                                            | JPEG, JPG               | interpreted text, no<br>Endian issue) |

| IBM PowerPC*          | Bi-Endian           | PCX (PC Paintbrush*)                                                | MacPaint                | POV (Persistence of                   |

| Intel® 80x86          | Little-Endian       | QTM (MAC Quicktime*)                                                | SGI (Silicon Graphics*) | Visionraytracer*)                     |

| Intel® IXP network    | Bi-Endian           | RTF (Rich Text Format)                                              | Sun Raster              | RIFF (WAV & AVI*)                     |

| processors            |                     |                                                                     | WPG (WordPerfect*)      | TIFF                                  |

| Intel® Itanium®       | Bi-Endian           |                                                                     |                         | XWD (X Window Dump*)                  |

| processor family      |                     | Bus Protocols                                                       | Network Protocols       | Bus Protocols                         |

| Java Virtual Machine* | Big-Endian          | Infiniband                                                          | TCP/IP                  | GMII (8 bit wide bus, no              |

| MIPS*                 | Bi-Endian           | PCI Express                                                         | UDP                     | Endian issue)                         |

| Motorola 68k*         | Big-Endian          | PCI-32/PCI-64                                                       |                         |                                       |

| Sun SPARC*            | Big-Endian          | USB                                                                 |                         |                                       |

# **Endian-Neutral Approaches**

### **#** Conversion

🗠 Byte Swap

△ Network I/O Macro

# "Endian Neutral": allowing the code to be ported easily between processors of different Endian-architectures, and without rewriting any code. Endian-neutral software is developed by identifying system memory and external data interfaces, and using Endianneutral coding practices to implement the interfaces.

#### **HOMEWORK #2**

- Technical Report on "Endian-Neutral Approaches"

- ☑ What? Why? How?

- 2 3 pages; 1" margin all sides; 11 pt; Times New Roman; No cover page (Title and your name at the top, and start in the first page); single space; single column; again the importance of the first paragraph. No figure, no photo, text only.

Submission: Hardcopy only by 5:00pm Thursday 10/10/2012. 53 53