## PIC16F877 Instruction Set

# PIC – INSTRUCTION SET

WWW.MWFTR.COM

# Dr. Charles J. Kim

Howard University

# F877 Instruction Set

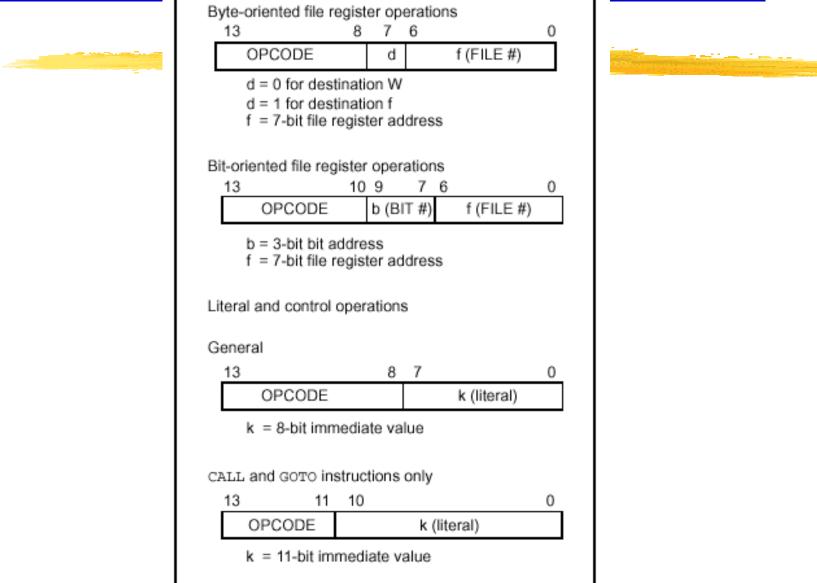

#### ∺ 14-Bit Word

#### **Byte-Oriented Instruction**

- ☑ F: File Register (or RAM)

- D: Destination

- $\boxtimes$ D=0: Destination  $\rightarrow$  W

- $\boxtimes$ D=1: Destination  $\rightarrow$  File Register

#### **Bit-Oriented Instruction**

- B: Bit Field

### Hiteral and Control Operation

K: 8-bit constant

# General Form of Instruction

#### Instruction List

| Mnemonic,   | Description                  |         |       | 14-Bit ( | Opcode | •    | Status   | Notes |

|-------------|------------------------------|---------|-------|----------|--------|------|----------|-------|

| Operands    | Description                  | Cycles  | MSb   |          |        | LSb  | Affected | Notes |

|             | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIO | NS       |        |      |          |       |

| ADDWF f, d  | Add W and f                  | 1       | 0.0   | 0111     | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF f, d  | AND W with f                 |         | 00    | 0101     | dfff   | ffff | Z        | 1,2   |

| CLRF f      | Clear f                      | 1       | 0.0   | 0001     | lfff   | ffff | Z        | 2     |

| CLRW -      | Clear W                      | 1       | 0.0   | 0001     | 0xxx   | xxxx | Z        |       |

| COMF f, d   | Complement f                 | 1       | 0.0   | 1001     | dfff   | ffff | Z        | 1,2   |

| DECF f, d   | Decrement f                  | 1       | 0.0   | 0011     | dfff   | ffff | Z        | 1,2   |

| DECFSZ f, d | Decrement f, Skip if 0       | 1(2)    | 0.0   | 1011     | dfff   | ffff |          | 1,2,3 |

| INCF f, d   | Increment f                  | 1       | 0.0   | 1010     | dfff   | ffff | Z        | 1,2   |

| INCFSZ f, d | Increment f, Skip if 0       | 1(2)    | 0.0   | 1111     | dfff   | ffff |          | 1,2,3 |

| IORWF f, d  | Inclusive OR W with f        | 1       | 0.0   | 0100     | dfff   | ffff | Z        | 1,2   |

| MOVF f, d   | Move f                       | 1       | 0.0   | 1000     | dfff   | ffff | Z        | 1,2   |

| MOVWF f     | Move W to f                  | 1       | 0.0   | 0000     | lfff   | ffff |          |       |

| NOP -       | No Operation                 | 1       | 0.0   | 0000     | 0xx0   | 0000 |          |       |

| RLF f, d    | Rotate Left f through Carry  | 1       | 0.0   | 1101     | dfff   | ffff | С        | 1,2   |

| RRF f, d    | Rotate Right f through Carry | 1       | 00    | 1100     | dfff   | ffff | С        | 1,2   |

| SUBWF f, d  | Subtract W from f            | 1       | 0.0   | 0010     | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF f, d  | Swap nibbles in f 1 00 11    |         |       |          | dfff   | ffff |          | 1,2   |

| XORWF f, d  | Exclusive OR W with f        | 1       | 0.0   | 0110     | dfff   | ffff | Z        | 1,2   |

|             | BIT-ORIENTED FILE REGIST     | ER OPER | ATION | IS       |        |      |          |       |

| BCF f, b    | Bit Clear f                  | 1       | 01    | 00bb     | bfff   | ffff |          | 1,2   |

| BSF f, b    | Bit Set f                    | 1       | 01    | 01bb     | bfff   | ffff |          | 1,2   |

| BTFSC f, b  | Bit Test f, Skip if Clear    | 1 (2)   | 01    | 10bb     | bfff   | ffff |          | 3     |

| BTFSS f, b  | Bit Test f, Skip if Set      | 1 (2)   | 01    | 11bb     | bfff   | ffff |          | 3     |

|             | LITERAL AND CONTROL          | OPERATI | ONS   |          |        |      |          |       |

| ADDLW k     | Add literal and W            | 1       | 11    |          | kkkk   |      | C,DC,Z   |       |

| ANDLW k     | AND literal with W           | 1       | 11    |          | kkkk   |      | Z        |       |

| CALL k      | Call subroutine              | 2       | 10    | 0kkk     | kkkk   | kkkk |          |       |

| CLRWDT -    | Clear Watchdog Timer         | 1       | 0.0   |          | 0110   |      | TO,PD    |       |

| GOTO k      | Go to address                | 2       | 10    | 1kkk     | kkkk   |      |          |       |

| IORLW k     | Inclusive OR literal with W  | 1       | 11    | 1000     | kkkk   |      | Z        |       |

| MOVLW k     | Move literal to W            | 1       | 11    |          | kkkk   |      |          |       |

| RETFIE -    | Return from interrupt        | 2       | 0.0   | 0000     | 0000   |      |          |       |

| RETLW k     | Return with literal in W     | 2       | 11    | 01xx     | kkkk   |      |          |       |

| RETURN -    | Return from Subroutine       | 2       | 00    | 0000     |        | 1000 |          |       |

| SLEEP -     | Go into standby mode         | 1       | 0.0   | 0000     | 0110   | 0011 | TO,PD    |       |

| SUBLW k     | Subtract W from literal      | 1       | 11    |          | kkkk   | kkkk | C,DC,Z   |       |

| XORLW k     | Exclusive OR literal with W  | 1       | 11    | 1010     | kkkk   | kkkk | Z        |       |

## Destination of the result

Harphi D=0: Destination  $\rightarrow$  W

HD=1: Destination  $\rightarrow$  File Register (Default)

### 🗠 addwf PORTD

☑Add content of PORTD to content of the W and store the result back into PORTD

#### Addwf PORTD, 0 ;

☑Add content of PORTD to content of the W and store the result into W

## **Register Addressing Modes**

## **#Immediate Addressing**

⊠(ex) MOVLW 0x0F

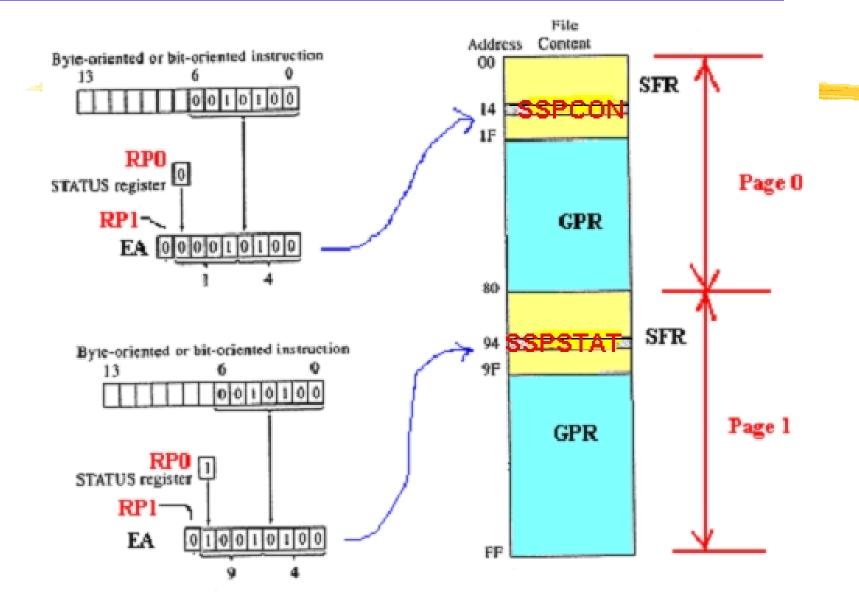

### **#**Direct Addressing

- ☐Uses 7 bits of 14 bit instruction to identify a register file address

- △8<sup>th</sup> and 9<sup>th</sup> bit comes from RPO and RP1 bits of STATUS register.

- (ex) SSPCON EQU 0x14

STATUS EQU 0x03

SSPSTAT EQU 0x94

BCF STATUS, 0x05

BCF SSPCON, 0x01

BSF STATUS, 0x05

- BCF SSPSTAT, 0x02

## **Direct Addressing**

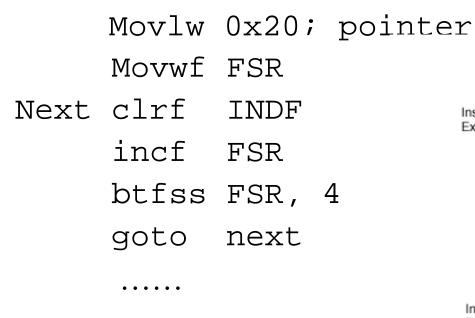

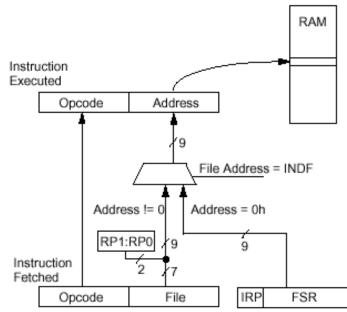

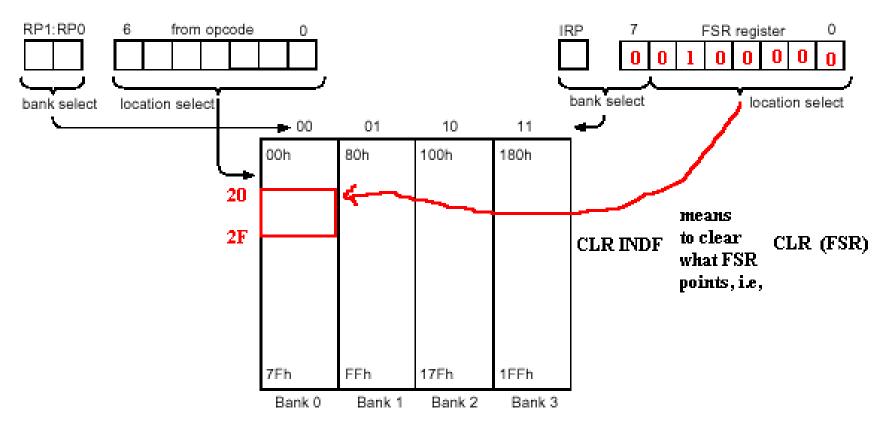

# Indirect Addressing

₭ INDF register

Any instruction using the INDF actually accesses the register pointed to by the File Select Register (FSR).

- # A 9-bit EA is obtained by concatenating the 8-bit FSR register and the IRP bit(STATUS<7>)

- ₭ Example: Erase the RAM section of 0x20-0x2F

# Direct vs. Indirect Addressing

#### DIRECT ADDRESSING

INDIRECT ADDRESSING

#### Instruction Sets -description convention

| Field         | Description                                                                                                                                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                          |

| W             | Working register (accumulator)                                                                                                                                |

| b             | Bit address within an 8-bit file register (0 to 7)                                                                                                            |

| k             | Literal field, constant data or label (may be either an 8-bit or an 11-bit value)                                                                             |

| x             | Don't care (0 or 1)<br>The assembler will generate code with x = 0. It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d             | Destination select;<br>d = 0: store result in W,<br>d = 1: store result in file register f.                                                                   |

| dest          | Destination either the W register or the specified register file location                                                                                     |

| label         | Label name                                                                                                                                                    |

| TOS           | Top of Stack                                                                                                                                                  |

| PC            | Program Counter                                                                                                                                               |

| PCLATH        | Program Counter High Latch                                                                                                                                    |

| GIE           | Global Interrupt Enable bit                                                                                                                                   |

| WDT           | Watchdog Timer                                                                                                                                                |

| TO            | Time-out bit                                                                                                                                                  |

| PD            | Power-down bit                                                                                                                                                |

| []            | Optional                                                                                                                                                      |

| ()            | Contents                                                                                                                                                      |

| $\rightarrow$ | Assigned to                                                                                                                                                   |

| < >           | Register bit field                                                                                                                                            |

| ∈             | In the set of                                                                                                                                                 |

| italics       | User defined term (font is courier)                                                                                                                           |

# ADDLW

kkkk

| Syntax: | [ <i>label</i> ] ADDLW | k   |

|---------|------------------------|-----|

| Oymax.  |                        | L L |

1

1

C, DC, Z

11

111x

Operands:  $0 \le k \le 255$

Operation:  $(W) + k \rightarrow W$

Status Affected:

Encoding:

Description:

The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register.

kkkk

Words:

Cycles:

| Example1  | ADDLW 0x15                                   |

|-----------|----------------------------------------------|

|           | Before Instruction                           |

|           | $W = 0 \times 10$                            |

|           | After Instruction                            |

|           | W = 0x25                                     |

|           |                                              |

| Example 2 | ADDLW MYREG                                  |

| Example E |                                              |

|           | Before Instruction<br>W = 0x10               |

|           | Address of MYREG $\dagger = 0x37$            |

|           | MYREG is a symbol for a data memory location |

|           | After Instruction                            |

|           | W = 0x47                                     |

| Syntax:          | [label] ADDWF f,d                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                   |

| Operation:       | (W) + (f) $\rightarrow$ destination                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                             |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                    |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0 the result is a W register. If 'd' is 1 the result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                    |

| Cycles:          | 1 Example 1 ADDWF FSR, 0<br>Before Instruction<br>W = 0x17<br>FSR = 0xC2                                                                             |

| Example 1 | ADDWF FSR, 0                     |  |  |  |  |

|-----------|----------------------------------|--|--|--|--|

|           | Before Instruction               |  |  |  |  |

|           | W = 0x17                         |  |  |  |  |

|           | FSR = 0xC2                       |  |  |  |  |

|           | After Instruction                |  |  |  |  |

|           | W = 0xD9                         |  |  |  |  |

|           | FSR = 0xC2                       |  |  |  |  |

| Example 2 | ADDWF INDF                       |  |  |  |  |

|           | Before Instruction               |  |  |  |  |

|           | W = 0x17                         |  |  |  |  |

|           | FSR = 0xC2                       |  |  |  |  |

|           | Contents of Address (FSR) = 0x20 |  |  |  |  |

|           | After Instruction                |  |  |  |  |

|           | W = 0x17                         |  |  |  |  |

|           | FSR = 0xC2                       |  |  |  |  |

|           | Contents of Address (FSR) = 0x37 |  |  |  |  |

## ANDLW

| Syntax: [label]ANDLW k                                                                                                    |      |

|---------------------------------------------------------------------------------------------------------------------------|------|

| Operands: $0 \le k \le 255$                                                                                               |      |

| Operation: (W).AND. (k) $\rightarrow$ W                                                                                   |      |

| Status Affected: Z                                                                                                        |      |

| Encoding: 11 1001 kkkk kkkk                                                                                               |      |

| Description: The contents of W register are AND'ed with the eight bit literal 'k'. The resul<br>placed in the W register. | t is |

| Words: 1                                                                                                                  |      |

| Cycles: 1                                                                                                                 |      |

| Example 1 | ANDLW 0x5F                                                      |                                                                     |

|-----------|-----------------------------------------------------------------|---------------------------------------------------------------------|

|           | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03 | ; 0101 1111 (0x5F)<br>; 1010 0011 (0xA3)<br>;<br>; 0000 0011 (0x03) |

## ANDWF

#### AND W with f

| Syntax:          | [ label ] A      | NDWF                 | f,d        |                                            |                           |                                 |         |

|------------------|------------------|----------------------|------------|--------------------------------------------|---------------------------|---------------------------------|---------|

| Operands:        | $0 \le f \le 12$ | 7                    |            |                                            |                           |                                 |         |

|                  | $d \in [0,1]$    |                      |            |                                            |                           |                                 |         |

| Operation:       | (W).AND          | $(f) \rightarrow de$ | stination  | ı                                          |                           |                                 |         |

| Status Affected: | Z                |                      |            |                                            |                           |                                 |         |

| Encoding:        | 0.0              | 0101                 | dfff       | ffff                                       |                           |                                 |         |

| Description:     | AND the V        | / register           | with regis | ter 'f'. If 'd' is 0 t                     | the result is sto         | red in the W regist             | ter. If |

|                  | 'd' is 1 the     | result is s          | tored bac  | k in register 'f'.                         |                           |                                 |         |

| Words:           | 1                | Example              | 1          | ANDWF FSR                                  |                           |                                 |         |

| Cycles:          | 1                |                      |            | Before Instruction                         | on                        | ; 0001 0111                     | (0x17)  |

|                  |                  |                      |            |                                            |                           | ,                               |         |

|                  |                  |                      |            | W =                                        | 0x17                      | ; 1100 0010                     | (0xC2)  |

|                  |                  |                      |            | FSR =                                      | 0xC2                      | ; 1100 0010<br>;                |         |

|                  |                  |                      |            | FSR =<br>After Instruction                 | 0xC2                      | ; 1100 0010<br>;<br>; 0000 0010 |         |

|                  |                  |                      |            | FSR =<br>After Instruction<br>W =          | 0xC2<br>0x17              | ;                               | (0xC2)  |

|                  |                  |                      |            | FSR =<br>After Instruction                 | 0xC2<br>0x17              | ;                               | (0xC2)  |

|                  |                  | Example              | 2          | FSR =<br>After Instruction<br>W =          | 0xC2<br>0x17<br>0x02      | ;                               | (0xC2)  |

|                  |                  | Example              | 2          | FSR =<br>After Instruction<br>W =<br>FSR = | 0xC2<br>0x17<br>0x02<br>0 | ;                               | (0xC2)  |

FSR = 0xC2

W = 0x02FSR = 0xC2

After Instruction

(0x02)

\_ \_ \_ \_ \_ \_

; 0000 0010

| BCF              | Bit Clear f                    | Example 1 | BCF FLAG_REG, 7    |                     |

|------------------|--------------------------------|-----------|--------------------|---------------------|

| Syntax:          | [label]BCF f,b                 |           | Before Instruction |                     |

| Operands:        | $0 \le f \le 127$              |           | $FLAG_REG = 0xC7$  | ; <b>1</b> 100 0111 |

|                  | $0 \le b \le 7$                |           | After Instruction  |                     |

| Operation:       | $0 \rightarrow f \le b >$      |           | $FLAG_REG = 0x47$  | ; <b>0</b> 100 0111 |

| Status Affected: | None                           |           |                    |                     |

| Encoding:        | 01 00bb b                      | offf ffff |                    |                     |

| Description:     | Bit 'b' in register 'f' is cle | eared.    |                    |                     |

| Words:           | 1                              |           |                    |                     |

| Cycles:          | 1                              |           |                    |                     |

| BSF                            |                                              | Bit Set    | f         |      |                                                                                    |                     |

|--------------------------------|----------------------------------------------|------------|-----------|------|------------------------------------------------------------------------------------|---------------------|

| Syntax:<br>Operands:           | [ <i>label</i> ]E<br>0 ≤ f ≤ 12<br>0 ≤ b ≤ 7 | 27         |           |      | <ul> <li>BSF FLAG_REG, 7</li> <li>Before Instruction<br/>FLAG_REG =0x0A</li> </ul> | ; <b>0</b> 000 1010 |

| Operation:<br>Status Affected: | 1 → f <b></b>                                |            |           |      | After Instruction<br>FLAG_REG =0x8A                                                | ; <b>1</b> 000 1010 |

| Encoding:                      | 01                                           | 01bb       | bfff      | ffff |                                                                                    |                     |

| Description:                   | Bit 'b' in                                   | register ' | f is set. | ļ    |                                                                                    |                     |

| Words:                         | 1                                            |            |           |      |                                                                                    |                     |

| Cycles:                        | 1                                            |            |           |      |                                                                                    |                     |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                           |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0' then the next instruction is skipped.<br>If bit 'b' is '0' then the next instruction (fetched during the current instruction execu-<br>tion) is discarded, and a NOP is executed instead, making this a 2 cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                                              |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                           |

| Example 1        | HERE BTFSC FLAG, 4                                                                                                                                                                                                                                             |

| Example 1        | FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                             |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                        |                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSS f,b                                                                                                                                                                                                                               |                                                                                                                |

| Operands:        | 0 ≤ f ≤ 127<br>0 ≤ b < 7                                                                                                                                                                                                                       |                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                        | The second s |

| Status Affected: | None                                                                                                                                                                                                                                           |                                                                                                                |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                              |                                                                                                                |

| Description:     | If bit 'b' in register 'f' is '1' then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction (fetched during the current<br>tion execution) is discarded and a NOP is executed instead, mak<br>2 cycle instruction. |                                                                                                                |

| Words:           | 1                                                                                                                                                                                                                                              |                                                                                                                |

| Cycles:          | 1(2)                                                                                                                                                                                                                                           |                                                                                                                |

|                  | Afte                                                                                                                                                                                                                                           | PC = addressHERE<br>FLAG= xxx0 xxxx<br>r Instruction<br>Since FLAG<4>= 0,<br>PC = addressFALSE                 |

| Example 1        | TRUE •                                                                                                                                                                                                                                         | PC = addressHERE<br>FLAG= xxx1 xxxx<br>r Instruction<br>Since FLAG<4>=1,<br>PC = addressTRUE                   |

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                        |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                         |

| Description:     | Call Subroutine. First, the 13-bit return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH<4:3>. CALL is a two cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                                         |

| Example 1 | HERE CALL THERE      |

|-----------|----------------------|

|           | Before Instruction   |

|           | PC = AddressHERE     |

|           | After Instruction    |

|           | TOS = Address HERE+1 |

|           | PC = Address THERE   |

|           |                      |

| CLRF             | Clear f                                                             |                                     |

|------------------|---------------------------------------------------------------------|-------------------------------------|

| Syntax:          | [label]CLRF f                                                       |                                     |

| Operands:        | $0 \le f \le 127$ Example 1                                         | CLRF FLAG_REG                       |

| Operation:       | $\begin{array}{l} 00h \rightarrow f \\ 1 \rightarrow Z \end{array}$ | Before Instruction<br>FLAG_REG=0x5A |

| Status Affected: | Z                                                                   | FLAG_REG=0x00                       |

| Encoding:        | 00 0001 1fff ffff                                                   | Z = 1                               |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.      |                                     |

| Words:           | 1                                                                   |                                     |

| Cycles:          | 1                                                                   |                                     |

| CLRW             |                                          | Clear W    | ,         |            |      |           |   |

|------------------|------------------------------------------|------------|-----------|------------|------|-----------|---|

| Syntax:          | [ label ]                                | CLRW       |           |            |      |           | _ |

| Operands:        | None                                     |            |           |            |      | Example 1 |   |

| Operation:       | $00h \rightarrow W$<br>1 $\rightarrow Z$ | I          |           |            |      | Example 1 |   |

| Status Affected: | Z                                        |            |           |            |      |           |   |

| Encoding:        | 0.0                                      | 0001       | 0xxx      | xxxx       | ]    |           |   |

| Description:     | W registe                                | er is clea | red. Zero | bit (Z) is | set. |           |   |

| Words:           | 1                                        |            |           |            |      |           | L |

| Cycles:          | 1                                        |            |           |            |      |           |   |

| CLRW          |       |      |

|---------------|-------|------|

| Before Instru | uctio | n    |

| W             | =     | 0x5A |

| After Instruc | tion  |      |

| W             | =     | 0x00 |

| Z             | =     | 1    |

|               |       |      |

| COMF             | Complement f                                                                                                                                  | Example 1                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                              |                                    |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                      | COMF REG1, 0<br>Before Instruction |

| Operation:       | $(\overline{f}) \rightarrow destination$                                                                                                      | REG1= 0x13<br>After Instruction    |

| Status Affected: | Z                                                                                                                                             | REG1= 0x13                         |

| Encoding:        | 00 1001 dfff ffff                                                                                                                             | W = 0xEC                           |

| Description:     | The contents of register 'f' are 1's complemented. If 'd' is 0 the result stored in W. If 'd' is 1 the result is stored back in register 'f'. | is                                 |

| Words:           | 1                                                                                                                                             |                                    |

| Cycles:          | 1                                                                                                                                             |                                    |

| DECF             |                         | Decrem    | ent f                          |      |                                                 | Example 1                       |    |

|------------------|-------------------------|-----------|--------------------------------|------|-------------------------------------------------|---------------------------------|----|

| Syntax:          | [ label ]               | DECF f,   | d                              |      |                                                 | DECF CNT                        |    |

| Operands:        | 0 ≤ f ≤ 12<br>d ∈ [0,1] |           |                                |      |                                                 | Before Instruction<br>CNT = 0x0 | )1 |

| Operation:       | (f) - 1 $\rightarrow$   | destinati | on                             |      |                                                 | Z = 0                           |    |

| Status Affected: | Z                       |           |                                |      |                                                 | After Instruction<br>CNT = 0x0  | 0  |

| Encoding:        | 0.0                     | 0011      | dfff                           | ffff |                                                 | Z = 1                           |    |

| Description:     |                         | 0         | 'f'. If 'd' is<br>k in registe |      | It is stored in the W register. If 'd' is 1 the | 9                               |    |

| Words:           | 1                       |           |                                |      |                                                 |                                 |    |

| Cycles:          | 1                       |           |                                |      |                                                 | 20                              |    |

| DECFSZ           | Decrement f, Skip                                                                                                                           | if 0                                        |                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                          |                                             |                                                      |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                    |                                             |                                                      |

| Operation:       | (f) - 1 $\rightarrow$ destination; skip if r                                                                                                | esult = 0                                   |                                                      |

| Status Affected: | None                                                                                                                                        |                                             |                                                      |

| Encoding:        | 00 1011 dfff                                                                                                                                | ffff                                        |                                                      |

|                  | in the W register. If 'd' is 1 the<br>If the result is 0, then the new<br>instruction execution) is disc<br>ing this a 2 cycle instruction. | t instruction (fetche<br>arded and a NOP is | d during the current                                 |

| Words:           | 1                                                                                                                                           | Case 1:                                     | Before Instruction                                   |

| Cycles:          | 1(2)                                                                                                                                        |                                             | PC = address HERE<br>CNT = 0x01<br>After Instruction |

|                  |                                                                                                                                             |                                             | CNT = 0x00                                           |

| Example          |                                                                                                                                             |                                             | PC = address CONTINUE                                |

| HERE             | DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                  | Case 2:                                     | Before Instruction<br>PC = address HERE              |

| CONTINUE         |                                                                                                                                             |                                             | CNT = 0x02<br>After Instruction<br>CNT = 0x01        |

|                  |                                                                                                                                             |                                             | PC = address HERE + 1                                |

| GOTO             |                                  | Uncond     | litional B | ranch     |                                                                             |

|------------------|----------------------------------|------------|------------|-----------|-----------------------------------------------------------------------------|

| Syntax:          | [ label ]                        | GOTO       | k          |           |                                                                             |

| Operands:        | $0 \le k \le 2$                  | 047        |            |           |                                                                             |

| Operation:       | $k \rightarrow PC < PC < PCLATH$ |            | PC<12:1    | 1>        |                                                                             |

| Status Affected: | None                             |            |            |           |                                                                             |

| Encoding:        | 10                               | 1kkk       | kkkk       | kkkk      |                                                                             |

| Description:     |                                  | bits <10:0 | )>. The up | pper bits | e eleven bit immediate value is loaded<br>of PC are loaded from PCLATH<4:3> |

| Words:           | 1                                |            |            |           |                                                                             |

| Cycles:          | 2                                |            |            |           |                                                                             |

| INCF             |                         | Increme  | ent f |      |                                                         | Example           |           |

|------------------|-------------------------|----------|-------|------|---------------------------------------------------------|-------------------|-----------|

| Syntax:          | [ label ]               | INCF 1   | ,d    |      |                                                         | INCF CNT,         | 1         |

| Operands:        | 0 ≤ f ≤ 12<br>d ∈ [0,1] | 27       |       |      |                                                         | Before Instructio |           |

| Operation:       | (f) + 1 $\rightarrow$   | destinat | ion   |      |                                                         | Z =               | 0         |

| Status Affected: | Z                       |          |       |      |                                                         | After Instruction | -         |

| Encoding:        | 0.0                     | 1010     | dfff  | ffff |                                                         | CNT =<br>Z =      | 0x00<br>1 |

| Description:     |                         |          | 0     |      | f 'd' is 0 the result is placed in ack in register 'f'. | <u> </u>          |           |

| Words:           | 1                       |          |       |      |                                                         |                   |           |

| Cycles:          | 1                       |          |       |      |                                                         |                   |           |

| INCFSZ           | Increment f, Skip if 0                                                                    |                                                                                    |

|------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                        |                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                         |                                                                                    |

| Operation:       | (f) + 1 $\rightarrow$ destination, skip if result = (                                     | 0                                                                                  |

| Status Affected: | None                                                                                      |                                                                                    |

| Encoding:        | 00 1111 dfff ffff                                                                         |                                                                                    |

| Description:     | the W register. If 'd' is 1 the result is p<br>If the result is 0, then the next instruct | •                                                                                  |

| Nords:           | 1                                                                                         |                                                                                    |

| Cycles:          | 1(2)                                                                                      | Case 1: Before Instruction<br>PC = address HERE<br>CNT = 0xFF<br>After Instruction |

|                  | Example                                                                                   | CNT = 0x00<br>PC = address CONTINUE                                                |

|                  | Livalliple                                                                                |                                                                                    |

| IORLW            | Inclusive OR Literal with W                                                                                     | Example                       |

|------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                        | IORLW 0x35                    |

| Operands:        | $0 \le k \le 255$                                                                                               | Before Instruction            |

| Operation:       | (W).OR. $k \rightarrow W$                                                                                       | W = 0x9A<br>After Instruction |

| Status Affected: | Z                                                                                                               | W = 0xBF                      |

| Encoding:        | 11 1000 kkkk kkkk                                                                                               | Z = 0                         |

| Description:     | The contents of the W register is OR'ed with the eight bit literal 'k'. The result<br>placed in the W register. | is                            |

| Words:           | 1                                                                                                               |                               |

| Cycles:          | 1                                                                                                               |                               |

| IORWF            | Inclusive OR W with f                                                                                                                               | Example                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                   | IORWF RESULT, 0                                            |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                  | Before Instruction<br>RESULT=0x13<br>W = 0x91              |

| Operation:       | (W).OR. (f) $\rightarrow$ destination                                                                                                               | After Instruction                                          |

| Status Affected: | Z                                                                                                                                                   | $\begin{array}{rcl} RESULT=0x13\\ W &= & 0x93 \end{array}$ |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                   | Z = 0                                                      |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is platthe W register. If 'd' is 1 the result is placed back in register 'f'. | ced in                                                     |

| Words:           | 1                                                                                                                                                   |                                                            |

| Cycles:          | 1                                                                                                                                                   | 24                                                         |

| MOVLW            |                            | Move Li       | iteral to N | N          |                      |                   |                  |      | 1 |

|------------------|----------------------------|---------------|-------------|------------|----------------------|-------------------|------------------|------|---|

| Syntax:          | [ label ]                  | MOVLW         | / k         |            |                      |                   | Example          |      |   |

| Operands:        | $0 \le k \le 2$            | 55            |             |            |                      |                   | MOVLW 0x5.       | A    |   |

| Operation:       | $k \mathop{\rightarrow} W$ |               |             |            |                      |                   | After Instructio | n    |   |

| Status Affected: | None                       |               |             |            |                      |                   | W =              | 0x5A |   |

| Encoding:        | 11                         | 00xx          | kkkk        | kkkk       |                      |                   |                  |      | 1 |

| Description:     | The eight                  | bit literal ' | k' is loade | d into W r | egister. The don't c | ares will assembl | e as 0's.        |      |   |

| Words:           | 1                          |               |             |            |                      |                   |                  |      |   |

| Cycles:          | 1                          |               |             |            |                      |                   |                  |      |   |

| MOVF             | Move f                                                                                                                                                                                                                                 | Example                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                       | MOVF FSR, 0                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                     | Before Instruction<br>W = 0x00<br>FSR = 0xC2 |

| Operation:       | (f) $\rightarrow$ destination                                                                                                                                                                                                          | After Instruction                            |

| Status Affected: | Z                                                                                                                                                                                                                                      | W = 0xC2                                     |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                      | Z = 0                                        |

| Description:     | The contents of register 'f' is moved to a destination dependent status of 'd'. If 'd' = 0, destination is W register. If 'd' = 1, the destinate register 'f' itself. 'd' = 1 is useful to test a file register since statis affected. | tination is                                  |

| Words:           | 1                                                                                                                                                                                                                                      |                                              |

| Cycles:          | 1                                                                                                                                                                                                                                      | 25                                           |

| MOVWF            | Move W to f                                |                               |

|------------------|--------------------------------------------|-------------------------------|

| Syntax:          | [label] MOVWF f                            | Example<br>MOVWF OPTION REG   |

| Operands:        | $0 \le f \le 127$                          | Before Instruction            |

| Operation:       | $(W) \to f$                                | OPTION_REG=0xFF               |

| Status Affected: | None                                       | W = 0x4F<br>After Instruction |

| Encoding:        | 00 0000 1fff ffff                          | OPTION_REG=0x4F               |

| Description:     | Move data from W register to register 'f'. | W = 0x4F                      |

| Words:           | 1                                          |                               |

| Cycles:          | 1                                          |                               |

| NOP              | No Operation  |      |      |      |  |  |

|------------------|---------------|------|------|------|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |

| Operands:        | None          |      |      |      |  |  |

| Operation:       | No operation  |      |      |      |  |  |

| Status Affected: | None          |      |      |      |  |  |

| Encoding:        | 0.0           | 0000 | 0xx0 | 0000 |  |  |

| Description:     | No operation. |      |      |      |  |  |

| Words:           | 1             |      |      |      |  |  |

| Cycles:          | 1             |      |      |      |  |  |

| Example     |                                  |

|-------------|----------------------------------|

| HERE        | NOP                              |

| Before Ins  | truction                         |

| PC          | <ul> <li>address HERE</li> </ul> |

| After Instr | uction                           |

| PC          | = address HERE + 1               |

|             |                                  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                        |                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                               |                                                                                        |

| Operands:        | None                                                                                                                                                                                                                         |                                                                                        |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow$ GIE                                                                                                                                                                                |                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                         |                                                                                        |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                            |                                                                                        |

| Description:     | Return from Interrupt. The 13-bit address at the Top of Stack (TOS) is<br>loaded in the PC. The Global Interrupt Enable bit, GIE (INTCON<7>), is<br>automatically set, enabling Interrupts. This is a two cycle instruction. |                                                                                        |

| Words:           | 1                                                                                                                                                                                                                            | Example                                                                                |

| Cycles:          | 2                                                                                                                                                                                                                            | HERE CALL TABLE ; W contains table<br>; offset value<br>• ; W now has table value<br>• |

| RETLW            |                                                                                                                                                                                                                              | TABLE ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                      |

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                     | :                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                            | RETLW kn ; End of table                                                                |

| Operation:       | $k \rightarrow W;$<br>TOS $\rightarrow PC$                                                                                                                                                                                   | Before Instruction<br>W = 0x07<br>After Instruction                                    |

| Status Affected  | I: None                                                                                                                                                                                                                      | W = value of k8<br>PC = TOS = Address Here + 1                                         |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                            | 10 - 100 - Photosoficito - 1                                                           |

| Description:     | The W register is loaded with the eight bit literal 'k'. The pro<br>loaded 13-bit address at the Top of Stack (the return addre<br>two cycle instruction.                                                                    | •                                                                                      |

| Words:           | 1                                                                                                                                                                                                                            |                                                                                        |

| Cycles:          | 2                                                                                                                                                                                                                            | 27                                                                                     |

# RETURN

| Syntax:          | [ label ]           | RETUR | RN   |      |                                                                         |

|------------------|---------------------|-------|------|------|-------------------------------------------------------------------------|

| Operands:        | None                |       |      |      |                                                                         |

| Operation:       | $TOS \rightarrow P$ | С     |      |      |                                                                         |

| Status Affected: | None                |       |      |      |                                                                         |

| Encoding:        | 00                  | 0000  | 0000 | 1000 |                                                                         |

| Description:     |                     |       |      |      | is POPed and the top of the stack counter. This is a two cycle instruc- |

| Words:           | 1                   |       |      |      |                                                                         |

| Cycles:          | 2                   |       |      |      |                                                                         |

| RLF              | Rotate Left f through Carry                                                                                                                                                                         |                    |                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|

| Syntax:          | [ label ] RLF f,d                                                                                                                                                                                   | Example            |                |

| -                |                                                                                                                                                                                                     | RLF REG1,0         | )              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                          | Before Instruction |                |

| Operation:       | See description below                                                                                                                                                                               | REG1=              | 1110 0110<br>0 |

| Status Affected: | C                                                                                                                                                                                                   | After Instruction  | Ū.             |

| Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                   |                    | L10 0110       |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Car<br>Flag. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | TY C 1             | 00 1100        |

|                  | C Register f                                                                                                                                                                                        |                    |                |

| Words:           | 1                                                                                                                                                                                                   |                    |                |

| Cycles:          | 1                                                                                                                                                                                                   |                    |                |

| RRF              | Rotate Right f through Carry                                                                                                                                                                        |                    |                |

| Syntax:          | [label] RRF f,d                                                                                                                                                                                     | Example            |                |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                   | RRF RE             | G1,0           |

|                  | d ∈ [0,1]                                                                                                                                                                                           | Before Instruction |                |

| Operation:       | See description below                                                                                                                                                                               | REG1= 111          | .0 0110        |

| Status Affected: | C                                                                                                                                                                                                   |                    | x xxxx         |

| Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                   | <b>C</b> = 0       |                |

| Description:     | The contents of register 'f are rotated one bit to the right through the Carry                                                                                                                      | After Instruction  |                |

| -                | Flag. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is                                                                                                                 | REG1= 111          |                |

|                  | placed back in register 'f'.                                                                                                                                                                        |                    | .1 0011        |

|                  | C Register f                                                                                                                                                                                        | <b>C</b> = 0       |                |

| Words:           | 1                                                                                                                                                                                                   |                    |                |

| Cycles:          | 1                                                                                                                                                                                                   |                    | 29             |

|                  |                                                                                                                    | Example<br>SUBLW | 0x02                         |

|------------------|--------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|

| SUBLW            | Subtract W from Literal                                                                                            | Before Ins       | struction                    |

|                  |                                                                                                                    |                  | W = 0x01                     |

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                           |                  | C = x                        |

| Operands:        | 0 ≤ k ≤ 255                                                                                                        |                  | Z = x                        |

|                  |                                                                                                                    | After Instru     | ruction ; result is positive |

| Operation:       | $k - (W) \rightarrow W$                                                                                            |                  |                              |

| Status Affected: | C, DC, Z                                                                                                           |                  | W = 0x01<br>C = 1            |

| Encoding:        | 11 110x kkkk kkkk                                                                                                  |                  | Z = 0                        |

| Description:     | The W register is subtracted (2's complement method) from the literal 'k'. The result is placed in the W register. | he eight bit     |                              |

| Words:           | 1                                                                                                                  |                  |                              |

| Cycles:          | 1                                                                                                                  |                  |                              |

|                  |                                                                                                                                                                           | Example                            |