### **EECE 417 Computer Systems Architecture**

### Department of Electrical and Computer Engineering Howard University

**Charles Kim**

Spring 2007

# Computer Organization and Design (3<sup>rd</sup> Ed)

### -The Hardware/Software Interface

by

David A. Patterson John L. Hennessy

### **Chapter Five**

### **The Processor: Detapath and Control**

### Part B

## **Multi-Cycle Implementation**

- A Solution:

- use a "smaller" cycle time

- have different instructions take different numbers of cycles

- a "multicycle" datapath:

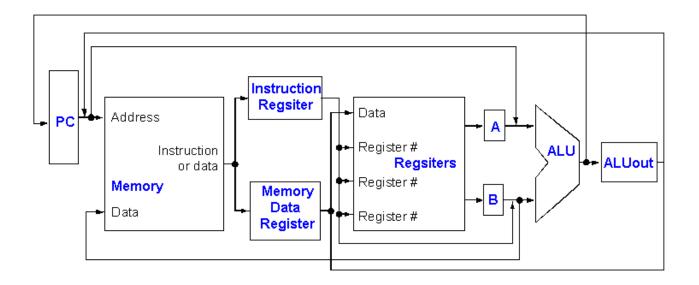

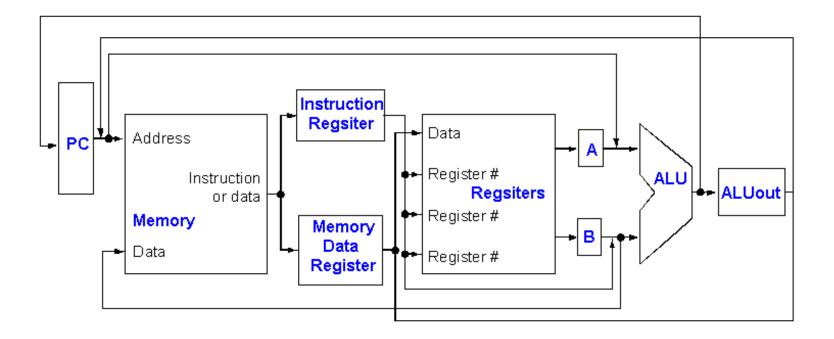

- Overview

- step: 1 clock cycle in execution

- Functional units allowed to be used more than once per instruction (as long as it is used on different clock cycle)

- Single memory unit (instruction and data)

- Single ALU (rather than ALU and two ADDs)

### **Overview of Multi-Cycle Approach (2)**

- Overview (-continued)

- One of more registers are added after every functional unit to hold the output until the value is used in a subsequent clock cycle

- At the end of clock, all data that is used in the subsequent clock cycle must be stored in a *state element*.

- Data used by <u>subsequent instructions</u> in a later clock cycle is stored into one of:

- Register File

- PC

- Memory

- Data used by the <u>same instruction</u> in a later clock must be stored into one of the added registers

- Added Temporary Registers

- IR (Instruction Register): save for instruction read

- MDR( Memory Data Register): save for data read

- A (Register A): register operand read from register file

- B (Register B): register operand read from register file

- ALUout (ALU output register): hold the output of ALU

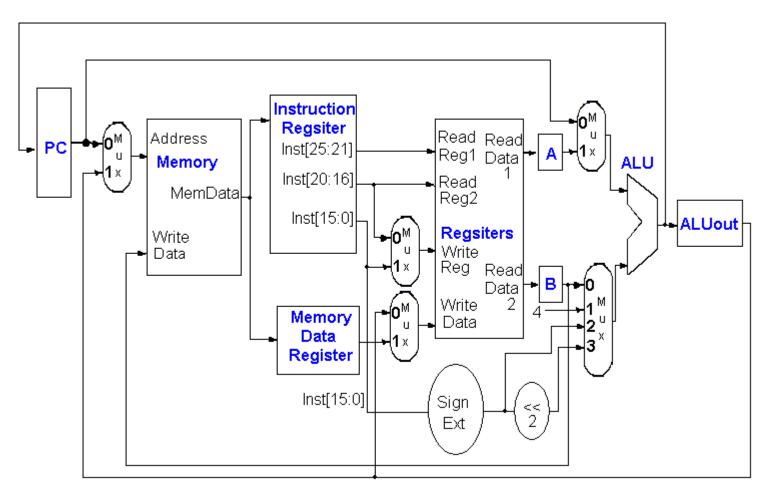

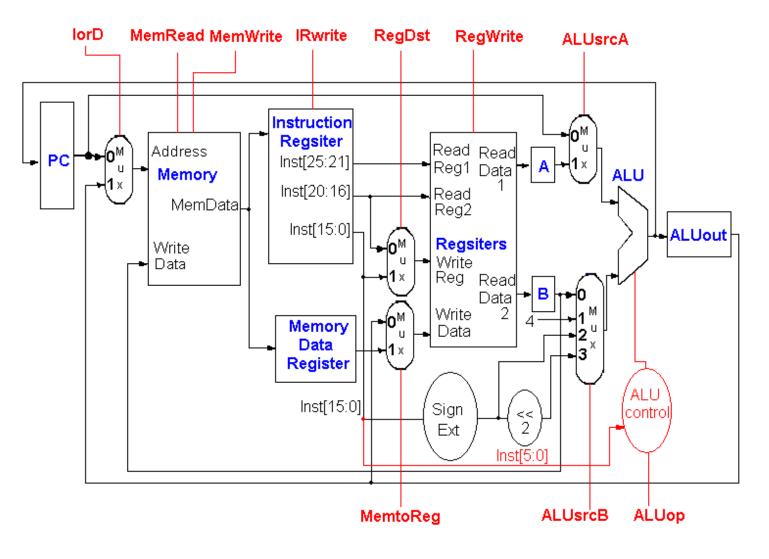

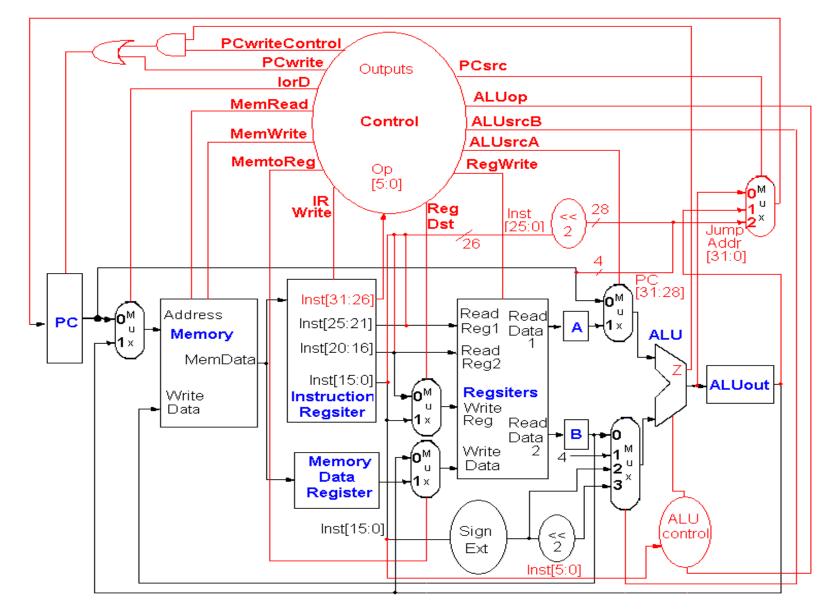

### Multiplxor for Multi-Cycle Approach

- Single Memory –Mem (from ALUout)/Inst (from PC))

- IR needs to hold the instruction until the end of execution

- Single ALU

### **Control Signals for Multi-Cycle Datapath**

- Jump instr is still not included -PC

- Controlled branch is not included PC

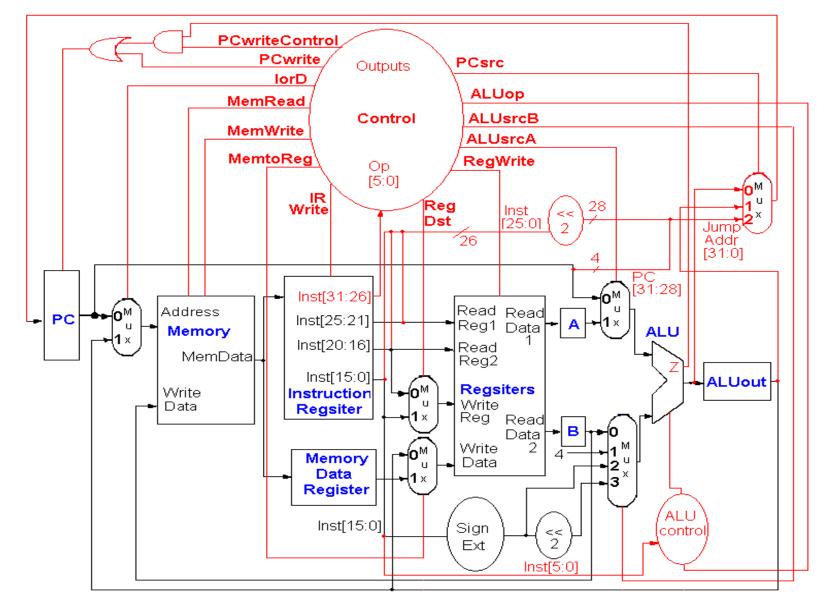

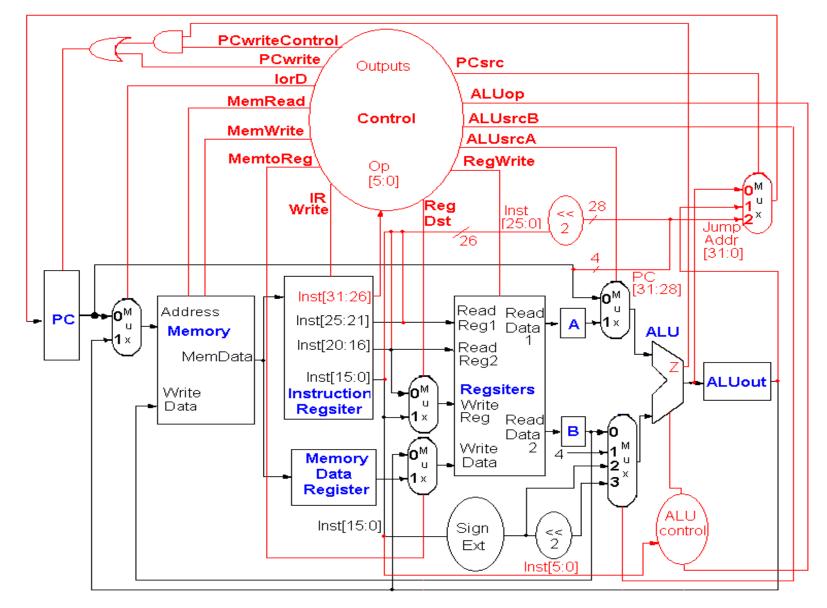

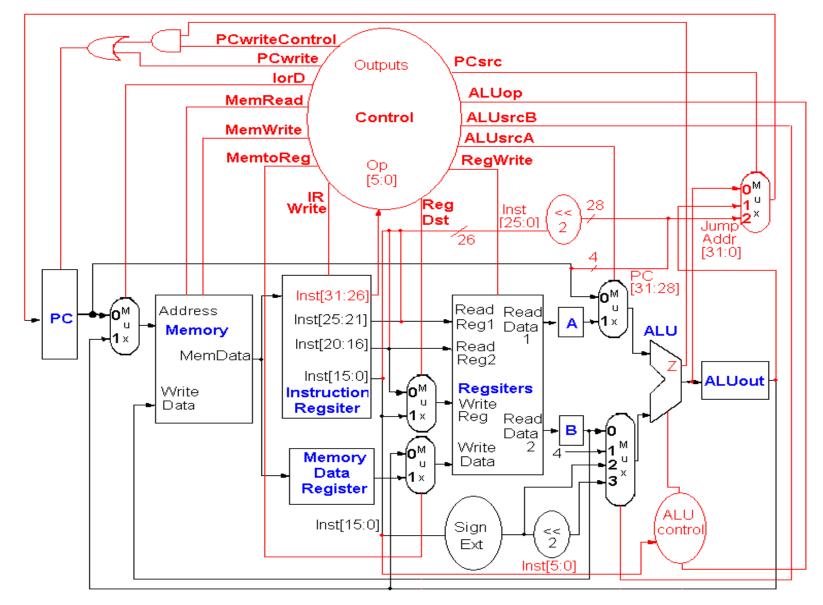

### **Complete Multipath Datapath and Control unit**

9

### **Control Signal Explanation (Tables. P.324)**

### Action of Control Signals (1-bit control signals)

11

### Action of Control Signals (2-bit signals)

### Instructions from ISA perspective – Clock Cycle

- What should happen in each clock cycle of the multicycle execution?

- Consider each instruction from perspective of ISA.

- Example:

- The add instruction changes a register.

- Register specified by bits 15:11 of instruction.

- Instruction specified by the PC.

- New value is the sum ("op") of two registers.

- Registers specified by bits 25:21 and 20:16 of the instruction

In order to accomplish this we must break up the instruction. (kind of like introducing variables when programming)

### **Breaking down an instruction**

• ISA definition of arithmetic:

- Could break down to:

- IR <= Memory[PC]

- A <= Reg[IR[25:21]]

- B <= Reg[IR[20:16]]

- ALUOut <= A op B

- Reg[IR[20:16]] <= ALUOut

- We forgot an important part of the definition of arithmetic!

- PC <= PC + 4

### Idea behind multicycle approach

- We define each instruction from the ISA perspective

- Break it down into steps following our rule that data flows through at most one major functional unit (e.g., balance work across steps)

- Introduce new registers as needed (e.g, A, B, ALUOut, MDR, etc.)

- Finally try and pack as much work into each step (avoid unnecessary cycles) while also trying to share steps where possible (minimizes control, helps to simplify solution)

- Result: Our book's multicycle Implementation!

### **Five Execution Steps**

- Instruction Fetch

- Instruction Decode and Register Fetch

- Execution, Memory Address Computation, or Branch Completion

- Memory Access or R-type instruction completion

- Write-back step

**INSTRUCTIONS TAKE FROM 3 - 5 CYCLES!**

# **Step 1: Instruction Fetch**

- Use PC to get instruction and put it in the Instruction Register.

- Increment the PC by 4 and put the result back in the PC.

- Can be described succinctly using RTL "Register-Transfer Language"

IR <= Memory[PC];

PC <= PC + 4;</pre>

Can we figure out the values of the control signals?

What is the advantage of updating the PC now?

### **Step 2: Instruction Decode and Register Fetch**

- Read registers rs and rt in case we need them

- Compute the branch address in case the instruction is a branch

- RTL:

A <= Reg[IR[25:21]]; B <= Reg[IR[20:16]]; ALUOut <= PC + (sign-extend(IR[15:0]) << 2);</pre>

• We aren't setting any control lines based on the instruction type (we are busy "decoding" it in our control logic)

## **Step 3 (instruction dependent)**

- ALU is performing one of three functions, based on instruction type

- Memory Reference:

ALUOut <= A + sign-extend(IR[15:0]);

• R-type:

ALUOut <= A op B;

• Branch:

if (A==B) PC <= ALUOut;

# Step 4 (R-type or memory-access)

• Loads and stores access memory

• R-type instructions finish

Reg[IR[15:11]] <= ALUOut;</pre>

The write actually takes place at the end of the cycle on the edge

### Write-back step

• Reg[IR[20:16]] <= MDR;

Which instruction needs this?

| Step name                                                 | Action for R-type<br>instructions                                                            | Action for memory-<br>reference instructions                     | Action for<br>branches      | Action for<br>jumps                      |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|------------------------------------------|--|--|

| Instruction fetch                                         | IR <= Memory[PC]<br>PC <= PC + 4                                                             |                                                                  |                             |                                          |  |  |

| Instruction decode/register fetch                         | A <= Reg [IR[25:21]]<br>B <= Reg [IR[20:16]]<br>ALUOUT <= PC + (sign-extend (IR[15:0]) << 2) |                                                                  |                             |                                          |  |  |

| Execution, address computation,<br>branch/jump completion | ALUOut <= A op B                                                                             | ALUOut <= A + sign-extend<br>(IR[15:0])                          | If (A == B)<br>PC <= ALUOUt | PC <= {PC [31:28],<br>(IR[25:0]],2'b00)} |  |  |

| Memory access or R-type<br>completion                     | Reg [IR[15:11]] <=<br>ALUOut                                                                 | Load: MDR <= Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] <= B |                             |                                          |  |  |

| Memory read completion                                    |                                                                                              | Load: Reg[IR[20:16]] <= MDR                                      |                             |                                          |  |  |

**FIGURE 5.30** Summary of the steps taken to execute any instruction class. Instructions take from three to five execution steps. The first two steps are independent of the instruction class. After these steps, an instruction takes from one to three more cycles to complete, depending on the instruction class. The empty entries for the Memory access step or the Memory read completion step indicate that the particular instruction class takes fewer cycles. In a multicycle implementation, a new instruction will be started as soon as the current instruction completes, so these cycles are not idle or wasted. As mentioned earlier, the register file actually reads every cycle, but as long as the IR does not change, the values read from the register file are identical. In particular, the value read into register B during the Instruction decode stage, for a branch or R-type instruction, is the same as the value stored into B during the Execution stage and then used in the Memory access stage for a store word instruction.

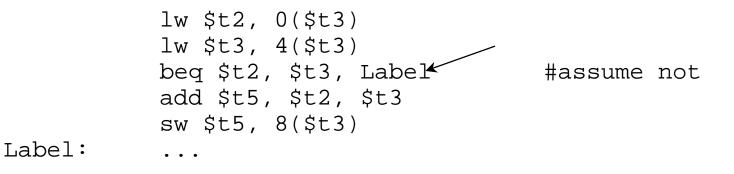

### **Simple Questions**

- Loads (5), Stores(4), ALU instructions (4), Branches(3), Jumps(3)

- How many cycles will it take to execute this code?

- What is going on during the 8th cycle of execution?

- In what cycle does the actual addition of \$t2 and \$t3 takes place?

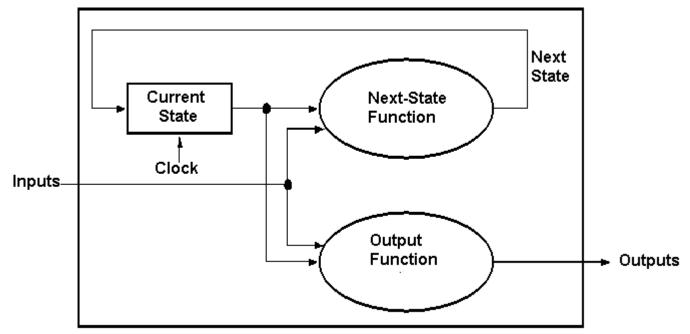

# Specification of the Multicycle Control – Finite State Machine (FSM) approach

- Finite state machines-A Sequential Logic Function

- a set of states and

- next state function (determined by current state and the input)

- output function (determined by current state and possibly input)

- We'll use a Moore machine (output based only on current state)

- If the output function can depend on both the <u>current state</u> and the <u>current input</u>, the machine is called a *Mealy machine*.

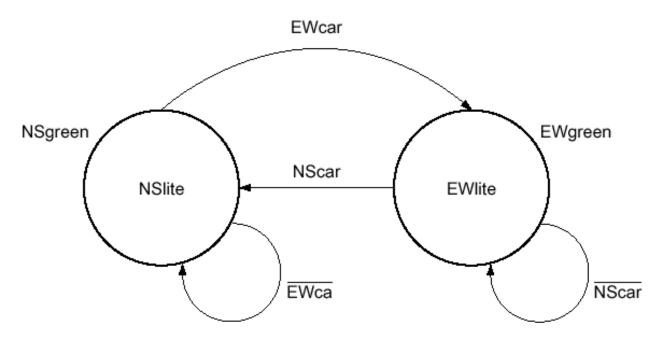

## FSM Example - controlling a traffic light

- Our example concerns the control of a traffic light at an intersection of a north-south route and an east-west route. For simplicity, we will consider only the green and red lights. We want the lights to cycle no faster than 30 seconds in each direction, so we will use a 0.033 Hz clock so that the machine cycles between states at no faster than once every 30 seconds.

- There are two output signals:

- NSlite: When this signal is asserted, the light on the northsouth road is green; when this signal is deasserted the light on the north-south road is red.

- *EWlite:* When this signal is asserted, the light on the east-west road is green; when this signal is deasserted the light on the east-west road is red.

- There are two inputs: NScar and EWcar.

- NScar: Indicates that a car is over the detector placed in the roadbed in front of the light on the north-south road (going north or south).

- *EWcar:* Indicates that a car is over the detector placed in the roadbed in front of the light on the east-west road (going east or west).

# **FSM Example - continued**

- The traffic light should change from one direction to the other only if a car is waiting to go in the other direction; otherwise, the light should continue to show green in the same direction as the last car that crossed the intersection.

- To implement this simple traffic light we need two states:

- **NSgreen**: The traffic light is green in the north-south direction.

- **EWgreen**: The traffic light is green in the east-west direction.

|               | Inputs |       |            |

|---------------|--------|-------|------------|

| Current state | NScar  | EWcar | Next state |

| NSgreen       | 0      | 0     | NSgreen    |

| NSgreen       | 0      | 1     | EWgreen    |

| NSgreen       | 1      | 0     | NSgreen    |

| NSgreen       | 1      | 1     | EWgreen    |

| EWgreen       | 0      | 0     | EWgreen    |

| EWgreen       | 0      | 1     | EWgreen    |

| EWgreen       | 1      | 0     | NSgreen    |

| EWgreen       | 1      | 1     | NSgreen    |

### **FSM Example - Continued**

• the output function:

|               | Outputs |        |  |

|---------------|---------|--------|--|

| Current state | NSlite  | EWlite |  |

| NSgreen       | 1       | 0      |  |

| EWgreen       | 0       | 1      |  |

• Graphical Representation

# **FSM Example – Verilog version**

The next-state function would be given as

```

NextState = (CurrentState \cdot EWcar) + (CurrentState \cdot NScar)

```

where CurrentState is the contents of the state register (0 or 1) and NextState is the output of the next-state function that will be written into the state register at the end of the clock cycle.

The output function is also simple:

```

NSlite = CurrentState

EWlite = CurrentState

```

```

module TrafficLite (EWCar,NSCar,EWLite,NSLite,clock);

input EWCar, NSCar,clock;

output EWLite,NSLite;

reg state;

initial state=0; //set initial state

//following two assignments set the output, which is based only on the state

variable

assign NSLite = ~ state; //NSLite on if state = 0;

assign EWLite = state; //EWLite on if state =1

always @(posedge clock) // all state updates on a positive clock edge

case (state)

0: state = EWCar; //change state only if EWCar

1: state = NSCar; //change state only if NSCar

endcase

endmodule

```

• Example:

Appendix B. 37 A friend would like you to build an "electronic eye" for use as a fake security device. The device consists of three lights lined up in a row, controlled by the outputs Left, Middle, and Right, which, if asserted, indicate that a light should be on. Only one light is on at a time, and the light "moves" from left to right and then from right to left, thus scaring away thieves who believe that the device is monitoring their activity. Draw the graphical representation for the finite state machine used to specify the electronic eye. Note that the rate of the eye's movement will be controlled by the clock speed (which should not be too great) and that there are essentially no inputs.

### **FSM - Implementing the Control**

- Value of control signals is dependent upon:

- what instruction is being executed

- which step is being performed

- Use the information we've accumulated to specify a finite state machine

- specify the finite state machine graphically, or

- use microprogramming

- Implementation can be derived from specification

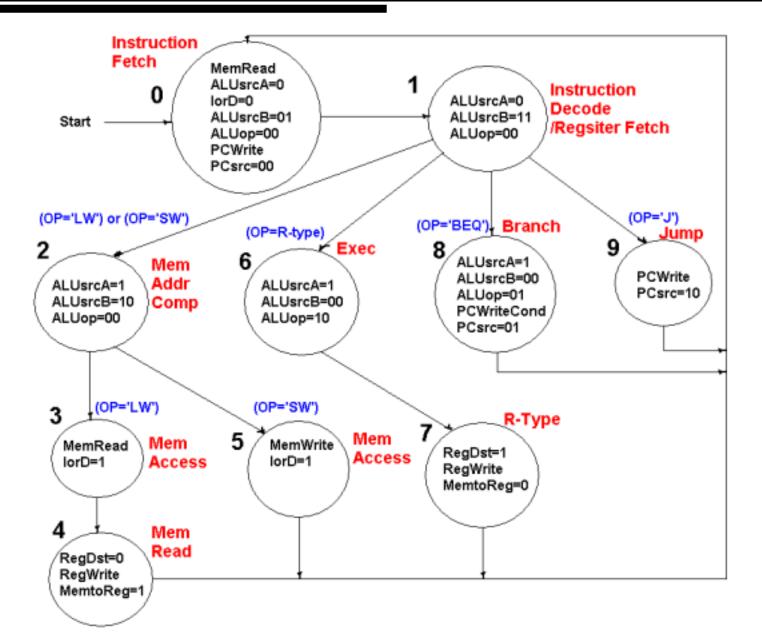

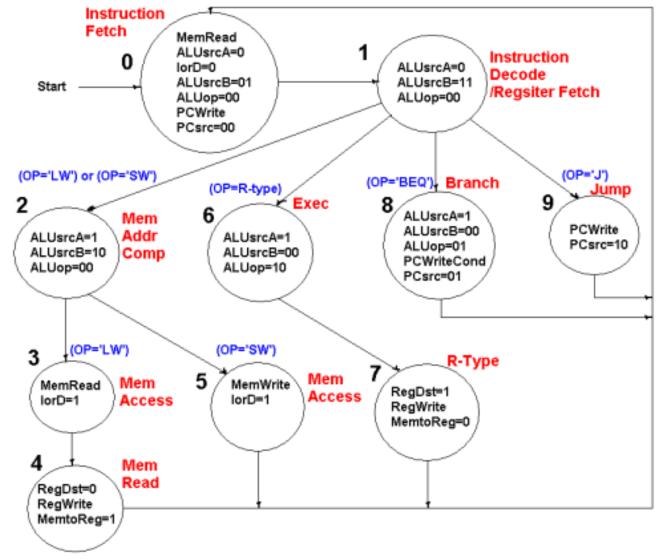

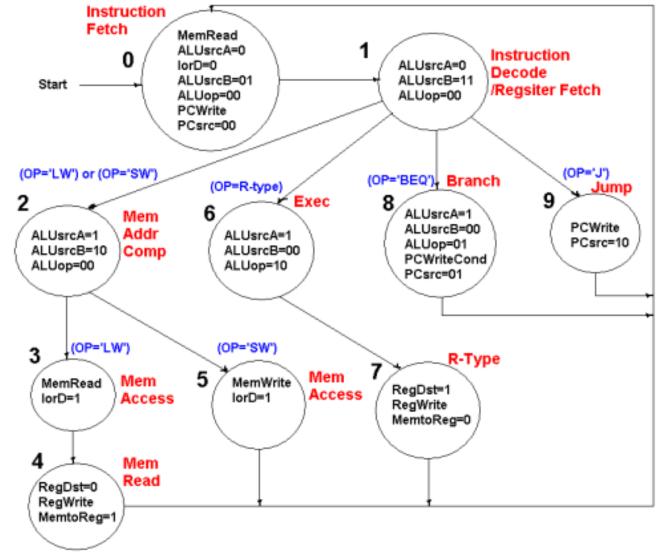

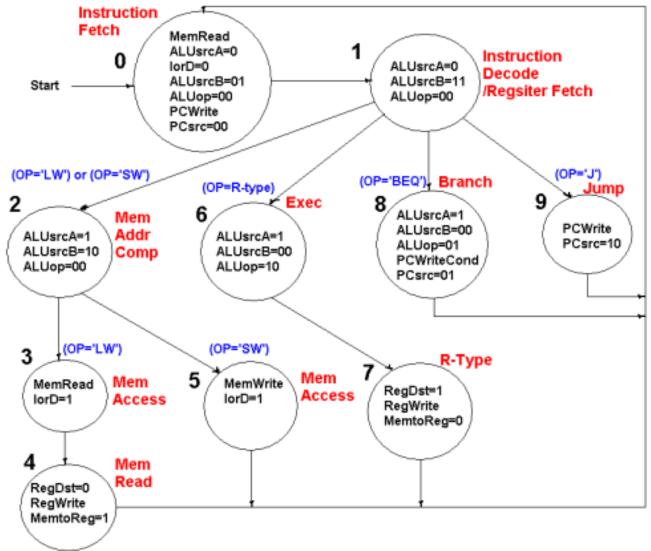

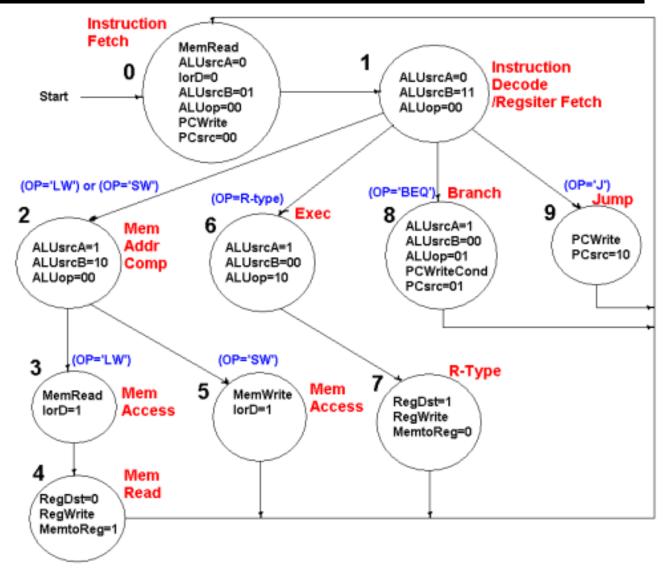

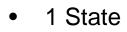

### **Graphical Specification of FSM**

## **Graphical Specification of FSM-Instruction Fetch and Decode**

- State 0

- State 1

- 4 Classes of instruction

- Mem ref

- R-type

- Beq

- Jump

## **Graphical Specification of FSM-Mem Reference Instructions**

- 4 States

- State 2

- Compute

Memory

Address

- In1: A Reg

- In2: Sign-Ext

- Out: ALUout

- State 3

- LW

- Mem Addr from ALU

- State 4

- Write to Reg

- State 5

- SW

- Mem Addr from ALU

### **Graphical Specification of FSM- R-type Instructions**

- 2 States

- State 6

In: 2 Regs

- State 7

- Register file to write

- Rd as destination

- ALUout is the source of the value to write into the register file

### **Graphical Specification of FSM- beq Instructions**

- 1 State

- State 8 – Compare reg A and reg B (read Zero output of ALU)

- PC set by the the ALUout

## **Graphical Specification of FSM- Jump Instruction**

- State 9

- Lower 26

bits of IR

- 00 for

lower

order bits

- Concatena ted with upper 4bits of PC

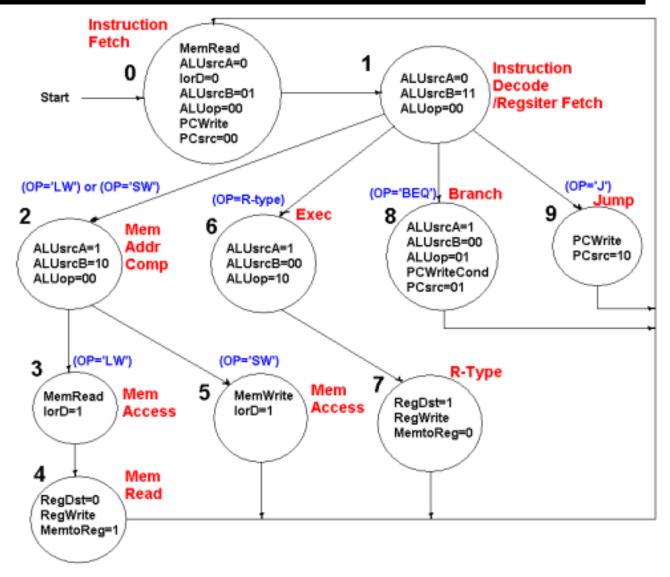

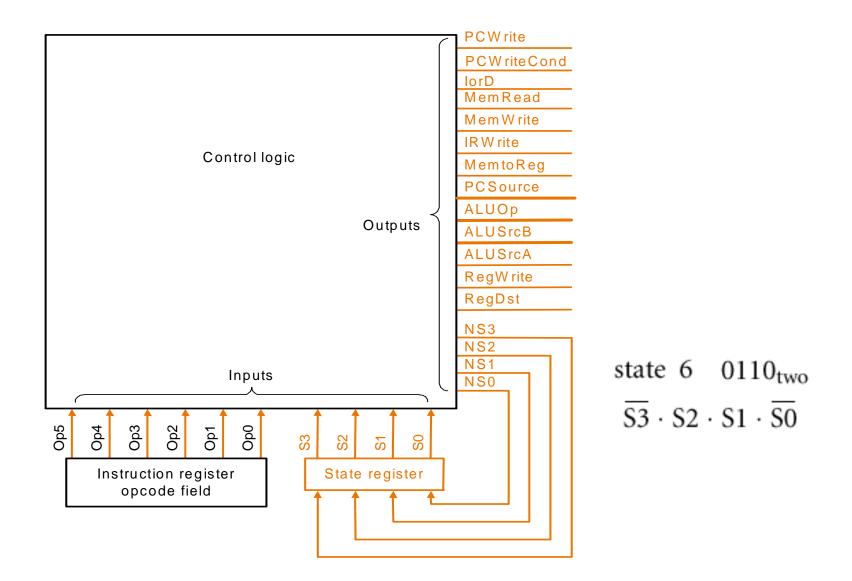

### **Finite State Machine Control – Moore Machine**

# **Logic Equations**

| Output      | Current states             |                 | Ор                                                                 |                                                                    |

|-------------|----------------------------|-----------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| PCWrite     | state0 + state9            |                 |                                                                    |                                                                    |

| PCWriteCond | state8                     |                 | _                                                                  |                                                                    |

| orD         | state3 + state5            | NextState1      | = State0 = $\overline{S3}$ ·                                       | $S2 \cdot S1 \cdot S0$                                             |

| MemRead     | state0 + state3            | NevtState3      | = State2 $\cdot$ (Op[5-                                            | -0 = 1w                                                            |

| MemWrite    | state5                     | Nextotateo      |                                                                    |                                                                    |

| IRWrite     | state0                     |                 | = S3 · S2 · S1 · S0                                                | $\overline{0} \cdot Op5 \cdot \overline{Op4} \cdot \overline{Op4}$ |

| MemtoReg    | state4                     | NevtState5      | = State $2 \cdot (Op[$                                             | $5_{-}0] = cw$                                                     |

| PCSource1   | state9                     | NextState5      |                                                                    |                                                                    |

| PCSource0   | state8                     |                 | $= \overline{S3} \cdot \overline{S2} \cdot S1 \cdot \overline{S0}$ | $0 \cdot Op5 \cdot Op4 \cdot O$                                    |

| ALUOp1      | state6                     | New+State7      | = State6 = $\overline{S3}$ .                                       | \$2 \$1 50                                                         |

| ALUOp0      | state8                     | NextState/      | = stated $=$ 55.                                                   | 52.51.50                                                           |

| ALUSrcB1    | state1 +state2             | NextState9      | = State1 $\cdot$ (Op[5                                             | 5-0] = jmp)                                                        |

| ALUSrcB0    | state0 + state1            |                 | $= \overline{S3} \cdot \overline{S2} \cdot \overline{S1} \cdot S0$ |                                                                    |

| ALUSICA     | state2 + state6 + state8   |                 | $= 53 \cdot 52 \cdot 51 \cdot 50$                                  | 0 · Op5 · Op4 · C                                                  |

| RegWrite    | state4 + state7            |                 |                                                                    |                                                                    |

| RegDst      | state7                     |                 |                                                                    |                                                                    |

| NextState0  | state4 + state5 + state7 + | state8 + state9 |                                                                    |                                                                    |

| NextState 1 | state0                     |                 |                                                                    |                                                                    |

| NextState2  | state1                     |                 | (Op = ' ] ⊌ ' ) +                                                  | (Op = '\$W')                                                       |

| NextState3  | state2                     |                 | (Op = ' ] ∀ ' )                                                    |                                                                    |

| NextState4  | state3                     |                 |                                                                    |                                                                    |

| NextState5  | state2                     |                 | (Op = "Sw")                                                        |                                                                    |

| NextState6  | state1                     |                 | (Op = 'R-type')                                                    |                                                                    |

| NextState7  | state6                     |                 |                                                                    |                                                                    |

| NextState8  | state1                     |                 | (Op = 'beq')                                                       |                                                                    |

| NextState9  | state1                     |                 | (Op = 'jmp')                                                       |                                                                    |

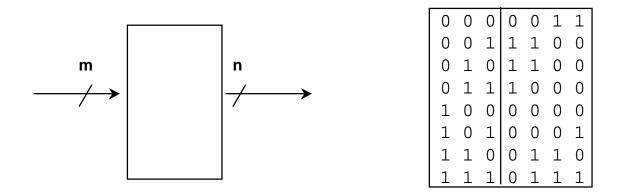

- ROM = "Read Only Memory"

- values of memory locations are fixed ahead of time

- A ROM can be used to implement a truth table

- if the address is m-bits, we can address  $2^{m}$  entries in the ROM.

- our outputs are the bits of data that the address points to.

m is the "height", and n is the "width"

• How many inputs are there?

6 bits for opcode, 4 bits for state = 10 address lines (i.e.,  $2^{10} = 1024$  different addresses)

# How many outputs are there? 16 datapath-control outputs, 4 state bits = 20 outputs

- ROM is  $2^{10} \times 20 = 20$ K bits (and a rather unusual size)

- Rather wasteful, since for lots of the entries, the outputs are the same

- i.e., opcode is often ignored

### **Truth Tables for Control Signals**

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 0  | 0         | 0  |

| 1  | 0  | 0         | 1  |

a. Truth table for PCWrite

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 0  | 0         | 0  |

| 0  | 0  | 1         | 1  |

d. Truth table for MemRead

| s3         | s2         | <b>s1</b> | s0 |

|------------|------------|-----------|----|

| 0          | 1          | 0         | 0  |

| ø Truth ta | ble for Me | mtoReg    |    |

g. Truth table for Memtokeg

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 1  | 1         | 0  |

### j. Truth table for ALUOp1

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 0  | 0         | 0  |

| 0  | 0  | 0         | 1  |

m. Truth table for ALUSrcBO

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 1  | 1         | 1  |

p. Truth table for RegDst

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 1  | 0  | 0         | 0  |

b. Truth table for PCWriteCond

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 1  | 0         | 1  |

e. Truth table for MemWrite

| s3          | s2          | <b>s1</b> | s0 |

|-------------|-------------|-----------|----|

| 1           | 0           | 0         | 1  |

| b. Touth to | ble for DCS | Source 4  |    |

h. Truth table for PCSource1

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 1  | 0  | 0         | 0  |

### k. Truth table for ALUOp0

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 0  | 1         | 0  |

| 0  | 1  | 1         | 0  |

| 1  | 0  | 0         | 0  |

### n. Truth table for ALUSrcA

| s3 | s2 | <b>s1</b> | s0 |

|----|----|-----------|----|

| 0  | 0  | 1         | 1  |

| 0  | 1  | 0         | 1  |

c. Truth table for lorD

| s3 | s2 | s1 | s0 |

|----|----|----|----|

| 0  | 0  | 0  | 0  |

f. Truth table for IRWrite

| s3           | s2         | s1     | s0 |

|--------------|------------|--------|----|

| 1            | 0          | 0      | 0  |

| i. Truth tab | le for PCS | ource0 |    |

| s3           | s2         | <b>s1</b> | s0 |

|--------------|------------|-----------|----|

| 0            | 0          | 0         | 1  |

| 0            | 0          | 1         | 0  |

| I. Truth tab | le for ALU | SrcB1     |    |

s2 s3 **s1** s0 0 0 0 1

1

1

1

o. Truth table for RegWrite

0

### **Truth Tables for Next-States**

| Op5 | Op4 | Op3 | Op2 | 0p1 | Op0 | \$3 | <b>S</b> 2 | <b>S1</b> | <b>S</b> 0 |

|-----|-----|-----|-----|-----|-----|-----|------------|-----------|------------|

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0          | 0         | 1          |

| 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0          | 0         | 1          |

a. The truth table for the NS3 output, active when the next state is 8 or 9. This signal is activated when the current state is 1.

| Op5 | Op4 | <b>Op</b> 3 | Op2 | Op1 | Op0 | \$3 | <b>S</b> 2 | <b>S1</b> | <b>S</b> 0 |

|-----|-----|-------------|-----|-----|-----|-----|------------|-----------|------------|

| 0   | 0   | 0           | 0   | 0   | 0   | 0   | 0          | 0         | 1          |

| 1   | 0   | 1           | 0   | 1   | 1   | 0   | 0          | 1         | 0          |

| Х   | Х   | Х           | Х   | Х   | Х   | 0   | 0          | 1         | 1          |

| х   | Х   | Х           | х   | х   | Х   | 0   | 1          | 1         | 0          |

b. The truth table for the NS2 output, which is active when the next state is 4, 5, 6, or 7. This situation occurs when the current state is one of 1, 2, 3, or 6.

| Op5 | Op4 | <b>O</b> p3 | Op2 | 0p1 | Op0 | \$3 | <b>S</b> 2 | <b>S1</b> | <b>S</b> 0 |

|-----|-----|-------------|-----|-----|-----|-----|------------|-----------|------------|

| 0   | 0   | 0           | 0   | 0   | 0   | 0   | 0          | 0         | 1          |

| 1   | 0   | 0           | 0   | 1   | 1   | 0   | 0          | 0         | 1          |

| 1   | 0   | 1           | 0   | 1   | 1   | 0   | 0          | 0         | 1          |

| 1   | 0   | 0           | 0   | 1   | 1   | 0   | 0          | 1         | 0          |

| Х   | Х   | Х           | Х   | Х   | Х   | 0   | 1          | 1         | 0          |

c. The truth table for the NS1 output, which is active when the next state is 2, 3, 6, or 7. The next state is one of 2, 3, 6, or 7 only if the current state is one of 1, 2, or 6.

| Op5 | Op4 | Op3 | Op2 | 0p1 | Op0 | \$3 | <b>S</b> 2 | <b>S1</b> | <b>S</b> 0 |

|-----|-----|-----|-----|-----|-----|-----|------------|-----------|------------|

| Х   | Х   | Х   | Х   | Х   | Х   | 0   | 0          | 0         | 0          |

| 1   | 0   | 0   | 0   | 1   | 1   | 0   | 0          | 1         | 0          |

| 1   | 0   | 1   | 0   | 1   | 1   | 0   | 0          | 1         | 0          |

| Х   | Х   | Х   | Х   | х   | Х   | 0   | 1          | 1         | 0          |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0          | 0         | 1          |

d. The truth table for the NSO output, which is active when the next state is 1, 3, 5, 7, or 9. This happens only if the current state is one of 0, 1, 2, or 6.

| Outputs     |      |      |      | Inp  | ut valu | es (S[3- | -0]) |      |      |      |

|-------------|------|------|------|------|---------|----------|------|------|------|------|

|             | 0000 | 0001 | 0010 | 0011 | 0100    | 0101     | 0110 | 0111 | 1000 | 1001 |

| PCWrite     | 1    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 0    | 1    |

| PCWriteCond | 0    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 1    | 0    |

| lorD        | 0    | 0    | 0    | 1    | 0       | 1        | 0    | 0    | 0    | 0    |

| MemRead     | 1    | 0    | 0    | 1    | 0       | 0        | 0    | 0    | 0    | 0    |

| MemWrite    | 0    | 0    | 0    | 0    | 0       | 1        | 0    | 0    | 0    | 0    |

| IRWrite     | 1    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 0    | 0    |

| MemtoReg    | 0    | 0    | 0    | 0    | 1       | 0        | 0    | 0    | 0    | 0    |

| PCSource1   | 0    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 0    | 1    |

| PCSource0   | 0    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 1    | 0    |

| ALUOp1      | 0    | 0    | 0    | 0    | 0       | 0        | 1    | 0    | 0    | 0    |

| ALUOp0      | 0    | 0    | 0    | 0    | 0       | 0        | 0    | 0    | 1    | 0    |

| ALUSrcB1    | 0    | 1    | 1    | 0    | 0       | 0        | 0    | 0    | 0    | 0    |

| ALUSrcB0    | 1    | 1    | 0    | 0    | 0       | 0        | 0    | 0    | 0    | 0    |

| ALUSrcA     | 0    | 0    | 1    | 0    | 0       | 0        | 1    | 0    | 1    | 0    |

| RegWrite    | 0    | 0    | 0    | 0    | 1       | 0        | 0    | 1    | 0    | 0    |

| RegDst      | 0    | 0    | 0    | 0    | 0       | 0        | 0    | 1    | 0    | 0    |

# **Tables for ROM implementation**

| Lower 4 bits of the address | Bits 19–4 of the word |  |  |

|-----------------------------|-----------------------|--|--|

| 0000                        | 100101000001000       |  |  |

| 0001                        | 00000000011000        |  |  |

| 0010                        | 00000000010100        |  |  |

| 0011                        | 001100000000000       |  |  |

| 0100                        | 000000100000010       |  |  |

| 0101                        | 001010000000000       |  |  |

| 0110                        | 000000001000100       |  |  |

| 0111                        | 00000000000011        |  |  |

| 1000                        | 010000010100100       |  |  |

| 1001                        | 100000010000000       |  |  |

|                         | Op [5-0]             |                        |                        |                       |                       |                    |  |

|-------------------------|----------------------|------------------------|------------------------|-----------------------|-----------------------|--------------------|--|

| Current state<br>S[3-0] | 000000<br>(R-format) | <b>000010</b><br>(jmp) | <b>000100</b><br>(beq) | <b>100011</b><br>(]w) | <b>101011</b><br>(SW) | Any other<br>value |  |

| 0000                    | 0001                 | 0001                   | 0001                   | 0001                  | 0001                  | 0001               |  |

| 0001                    | 0110                 | 1001                   | 1000                   | 0010                  | 0010                  | illegal            |  |

| 0010                    | XXXX                 | XXXX                   | XXXX                   | 0011                  | 0101                  | illegal            |  |

| 0011                    | 0100                 | 0100                   | 0100                   | 0100                  | 0100                  | illegal            |  |

| 0100                    | 0000                 | 0000                   | 0000                   | 0000                  | 0000                  | illegal            |  |

| 0101                    | 0000                 | 0000                   | 0000                   | 0000                  | 0000                  | illegal            |  |

| 0110                    | 0111                 | 0111                   | 0111                   | 0111                  | 0111                  | illegal            |  |

| 0111                    | 0000                 | 0000                   | 0000                   | 0000                  | 0000                  | illegal            |  |

| 1000                    | 0000                 | 0000                   | 0000                   | 0000                  | 0000                  | illegal            |  |

| 1001                    | 0000                 | 0000                   | 0000                   | 0000                  | 0000                  | illegal            |  |

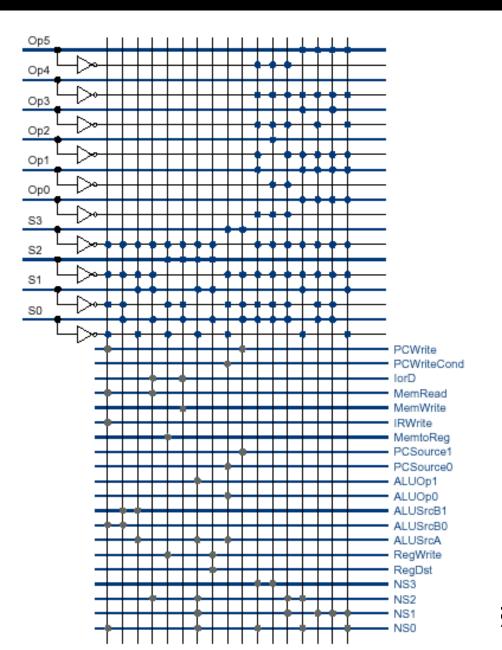

# **PLA Implementation**

- 17 unique Minterms

- 10 depends only on current states

- 7 on combination of O field and current-state bits

- Total Size of PLA

- (#inx#minterm) +

(#outx#minterm) =

(10x17)+(20x17) = 51(

### **ROM vs PLA**

- Break up the table into two parts

- 4 state bits tell you the 16 outputs,  $2^4 \times 16$  bits of ROM

- 10 bits tell you the 4 next state bits,  $2^{10} \times 4$  bits of ROM

- Total: 4.3K bits of ROM

- PLA is much smaller

- can share product terms

- only need entries that produce an active output

- can take into account don't cares

- Size is (#inputs × #product-terms) + (#outputs × #product-terms)

For this example = (10x17)+(20x17) = 510 PLA cells

- PLA cells usually about the size of a ROM cell (slightly bigger)